Hello TI Team,

We are using AM3352 with ISSI DDR3 "IS43TR16256A-125KBLI" in one of our project. We have used XDS200 USB Emulator in one of our project and able to connect the JTAG.

After connecting the JTAG and checking the Test connection we are getting the logs as follows:

[Start: Texas Instruments XDS2xx USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

D:\Users\kumar_ne\AppData\Local\TEXASI~1\

CCS\ti\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 560/2xx-class product.

This utility will load the program 'xds2xxu.out'.

The library build date was 'May 23 2017'.

The library build time was '19:03:48'.

The library package version is '6.0.628.3'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '13' (0x0000000d).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

This emulator does not create a reset log-file.

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End: Texas Instruments XDS2xx USB Debug Probe_0]

Going further with the reference of TI wiki processors.wiki.ti.com/.../Sitara_Linux_Training:_Tuning_the_DDR3_Timings_on_BeagleBoneBlack

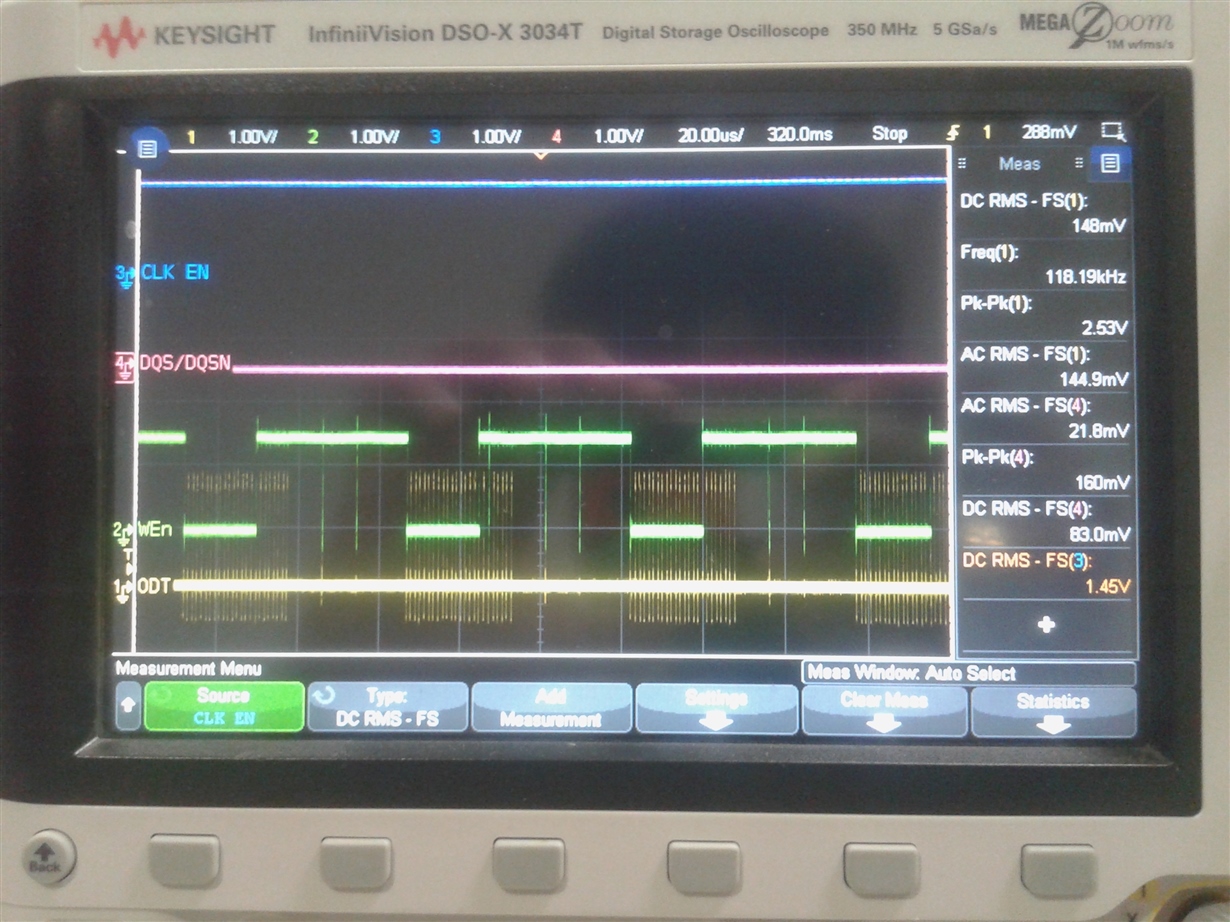

After uploading the customized gel file and downloaded . out file, we are unable to get the optimized DDR register optimized values.

Values are as follows:

[CortxA8]

Enter the PHY_INVERT_CLKOUT value (0 or 1) from the spreadsheet

0

Enter the Seed RD_DQS_SLAVE_RATIO Value in Hex to search the RD DQS Ratio Window

40

Enter the Seed FIFO_WE_SLAVE_RATIO Value in Hex to search the RD DQS Gate Window

8C

Enter the Seed WR_DQS_SLAVE_RATIO Write DQS Ratio Value in Hex to search the Write DQS Ratio Window

0

***************************************************************

The Slave Ratio Search Program Values are...

***************************************************************

PARAMETER MAX | MIN | OPTIMUM | RANGE

***************************************************************

DATA_PHY_RD_DQS_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

DATA_PHY_FIFO_WE_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

DATA_PHY_WR_DQS_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

DATA_PHY_WR_DATA_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

***************************************************************

rd_dqs_range = 0

fifo_we_range = 0

wr_dqs_range = 0

wr_data_range = 0

Optimal values have been found!!

***************************************************************

The Slave Ratio Search Program Values are...

***************************************************************

PARAMETER MAX | MIN | OPTIMUM | RANGE

***************************************************************

DATA_PHY_RD_DQS_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

DATA_PHY_FIFO_WE_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

DATA_PHY_WR_DQS_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

DATA_PHY_WR_DATA_SLAVE_RATIO 0x000 | 0x000 | 0x000 | 0x000

***************************************************************

===== END OF TEST =====

Please do let us know the probable solution here. Please suggest the resolution to resolve the issue.

8484.RatioSeed_AM335x_boards.xls8802.AM335x_DDR_register_calc_tool.xlsvector-eye_main-board_25_05_2017.pdf