Champs,

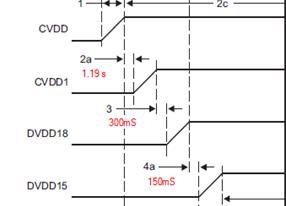

Customer has a product in production that has recently had a few failures in the field. The failures happen during DDR3 memory test when the DSP is at increased temperature (but still within spec: 55-65C). During investigation it has been found that when failure occurred the DSP clock did not switch from 66.6 Mhz to 666 Mhz as it is supposed to during boot which suggests failure with PLL initialization. At this moment the power sequence was closely inspected and it was found that the time between ramping rails is considerably bigger than what's recommended in the datasheet. Actual timing is shown below in red. the question is: could this longer timing between rails cause failure in PLL initialization?

thanks,Michael