Part Number: TMS320C6678

Team,

On our board the C6678 DSP works in memory boot mode. We gonna use the SPI flash as a boot source - avoiding the IBL usage. We've followed to http://processors.wiki.ti.com/index.php/File:C6678_directROM_boot_examples.zip steps to generate the SPI image and programmed it directly to SPI flash via an external programmer and soldered down the flash memory to our board. After it the DSP ROM boot loader successfully configures the device resources to start the boot process, loads the image from SPI flash into the device and stuck on RBL hand-over process so it still doesn't execute the image.

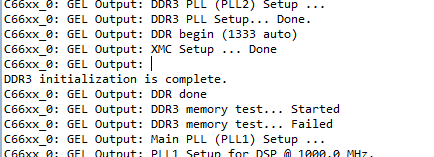

Next I tried to program the SPI flash via the C6678 DSP as described in manual. I used CCS and C:\ti\ccsv5\ccs_base\emulation\boards\evmc6678l\gel\evm6678l.gel as our board's .gel file to connect to our board but the .gel file did not match to our board, DDR3 test failed and the console gave next output:

At test time the DSP reads different values that it wrote before.

I tried to reconfigure the .gel file according to the SDRAM part's datasheet (since it differs from C6678 EVM's part) and the geometrical/timing specifications as described in the http://www.ti.com/lit/an/sprabl2e/sprabl2e.pdf KeyStone I DDR3 Initialization manual via the spreadsheets mentioned in this application report but have no success yet.

Could you please describe the most critical steps in this manual to let me correct the .gel file and mention the needed sources for you in case if we decide to ask you for .gel file calculation for our board on your side.

P.S.

Next are the core schematics differences between our board and TI's C6678 EVM reference board regarding to DDR3 memory controller:

- On our board the DDRSLRATE0 and DDRSLRATE1 channels are pulled down both with the 0 Om resistors (1 KOm pull up resistors are not loaded) while in the C6678 EVM the DDRSLRATE0 is pulled down with the 2 KOm resistor and the DDRSLRATE1 is pulled up with the 2 KOm

- The SDRAM parts used on our board is MT41K1G8SN-125 while the C6678 EVM uses K4B2G1646C-HCH9. We configured the DDR3 controller at 666.67MHz because of the errata on C6678 silicon but SDRAM part on our board is 800MHz speed grade part

- DDRAM fly-by problem.

- This note is from the EVM: Address/Command/Control/Clock routing must be Fly-By in byte order 0, 1, 2, 3 ECC, 4, 5, 6, 7.

- Our board's order is 0,1,2,3,ECC,7,6,5,4 so how read and write leveling handles this?

Please take a look to this and let us know in case if these differences can cause the above mentioned test failure. Additional questions:

- Still I can't understand why the DSP RBL stuck on hand-over process and doesn't execute the loaded image at first experiment when we write the SPI flash via the programmer

- Can we execute some instructions on DSP directly via JTAG interface without SPI flash and DRAM interaction?