Other Parts Discussed in Thread: CODECOMPOSER

Hello. We use 16-bit lpddr2 module (IS43LD16640C-25) with am4372 processor.

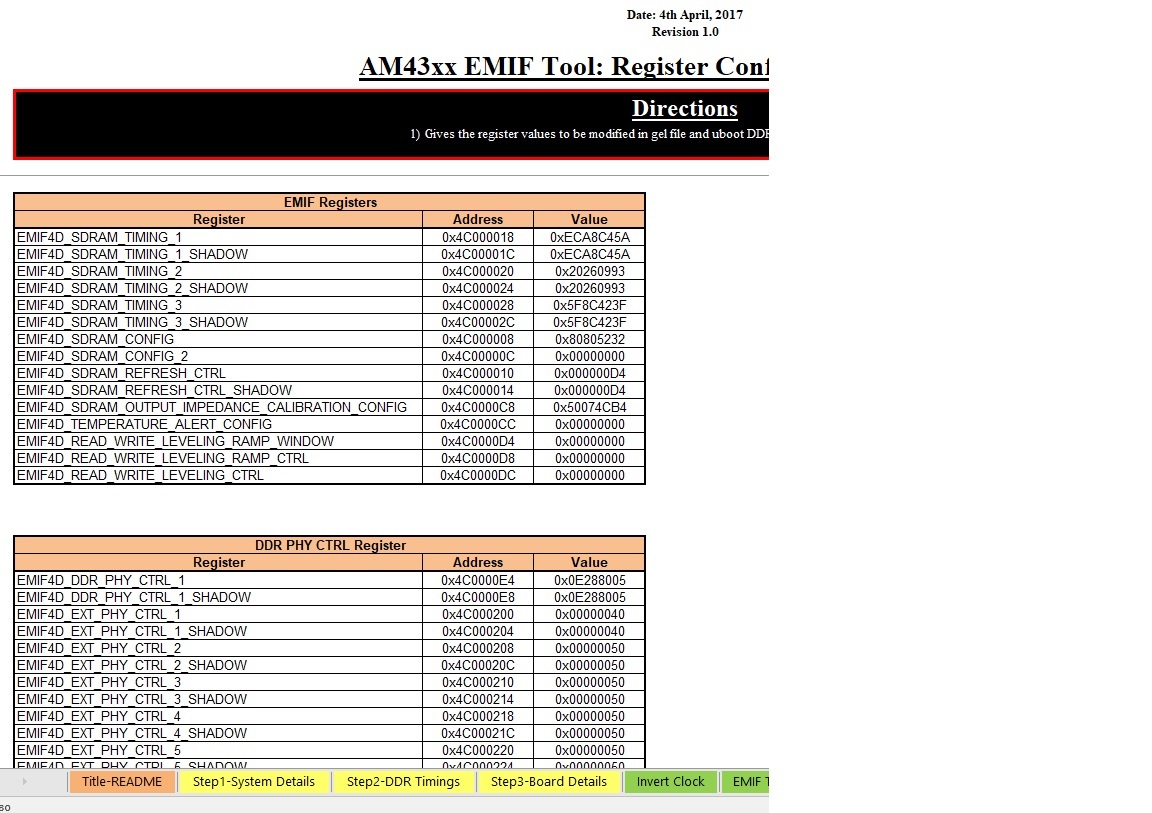

To configure EMIF we use "AM43xx EMIF Tools".

Calculated register values was written into gel-function to init EMIF when connected to core in CCS.

But DDR2 not work properly. In "CCS: memory view" at 0x80000000 and 16 bit config i look random (RRRR) words and work (OK) words:

0x80000000: RRRR RRRR RRRR RRRR OK OK OK OK

0x80000010: RRRR RRRR RRRR RRRR OK OK OK OK

0x80000020: RRRR RRRR RRRR RRRR OK OK OK OK

0x80000040: RRRR RRRR RRRR RRRR OK OK OK OK

.....

(OK) words write and read successfull, (RRRR) word read random values after refresh memory view window.

It's look as fail every four low address in eight. What configurable EMIF parameters may have this result?

We already check logical connection (not physical) between processor and LPDDR2. We have 2 board and both with some fail.