Part Number: AM4378

My company has designed a custom board based heavily on the AM437x Starter Kit. We have added an eMMC chip to the MMC1 port on the bootable pins (selected from the TRM to ensure bootability) and removed the conflicting connections from the starter kit on those lines. The sysboot configurations are setup for MMC0->MMC1->USB1->USB0 with a uSD card connected to MMC0 the same way as in the starter kit. Our customized device tree file is working for the kernel (version from tisdk 5.0.0.15) and once we're in the Linux environment when booting from the uSD card the eMMC is enumerated as mmcblk1 and is fully accessible.

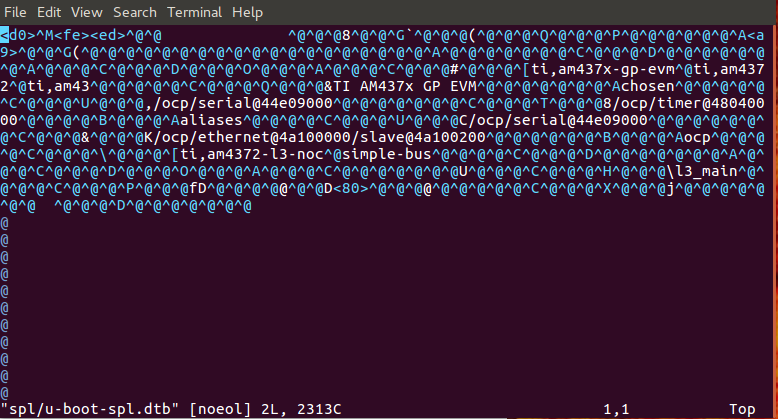

The issue is that I cannot seem to make the eMMC on MMC1 visible in the u-boot environment or from SPL. Since the MMC1 bus is working in the LInux environment I know the device tree is setup correctly in the Linux environment but when I try to point to that device tree to compile MLO and u-boot the SPL stage doesn't boot at all (nothing prints on power-up or system reset).

When the u-boot environment starts from the uSD card (using the default 'am437x-gp-evm' dtb file for compilation) it prints out the only found MMC device is MMC0 and when I execute "mmc dev 1" it reports nothing found. Here is the a copy of the terminal behavior from powering on the board with a uSD in the socket.

U-Boot SPL 2018.01-00228-g555fffa9f6-dirty (Sep 26 2018 - 11:35:14) Trying to boot from MMC1 SPL: Please implement spl_start_uboot() for your board SPL: Direct Linux boot not active! reading u-boot.img reading u-boot.img reading u-boot.img reading u-boot.img U-Boot 2018.01-00228-g555fffa9f6-dirty (Sep 26 2018 - 11:35:14 -0400) CPU : AM437X-GP rev 1.2 Model: TI AM437x SK EVM DRAM: 1 GiB PMIC: TPS65218 NAND: 0 MiB MMC: OMAP SD/MMC: 0 *** Warning - bad CRC, using default environment Net: <ethaddr> not set. Validating first E-fuse MAC cpsw, usb_ether Hit any key to stop autoboot: 0 => mmc list OMAP SD/MMC: 0 (SD) => mmc rescan => mmc list OMAP SD/MMC: 0 (SD) => mmc dev 1 MMC Device 1 not found no mmc device at slot 1

I reached my current point after formatting the eMMC within the Linux environment to be basically a copy of the uSD card. I created 2 partitions with start and stop sectors and fs types/bootable property that matched the card. Then I copied the boot partition contents from the uSD to the eMMC. I was also able to extract a fs image to the linux partition of the eMMC. With a known working MLO file on the eMMC's boot partion, trying to boot without the uSD card inserted results in this printout:

U-Boot SPL 2018.01-00228-g555fffa9f6-dirty (Sep 26 2018 - 12:10:32)

Trying to boot from MMC2 spl: could not find mmc device. error: -19 SPL: failed to boot from all boot devices ### ERROR ### Please RESET the board ###

I believe this indicates that I just need to create a working device tree for u-boot or SPL to use, that instantiates the MMC1 bus but I can't figure out why using my dts file that works under Linux breaks the hardware boot stage.

It is basically the opposite problem from this e2e thread except that our design has the uSD card on MMC0 and the eMMC on MMC1: