Tool/software: TI-RTOS

Hello, I'm a very newbie on AM5728.

I'm using IDK5728 for new project.(we will make a custom board after firmware test)

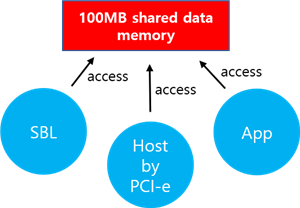

I have one data memory block(such as one large array or structure which is about 100MB).

I'd like to share this data memory between SBL, Application and Host(pci-e).

The idk5728 work as pci-e end point.(The custome board will be pci-e card)

My application will do many things with this data memory block.(calculate, read/write).

Actually, this memory block is almost main data memory for application.

Host will access this data memory very often by pci-e.

So, speed is important.

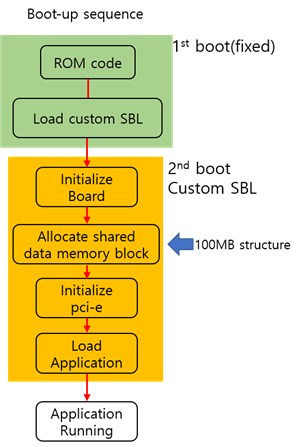

So, I think my boot-up sequence should be like this...

=Requirement is..

1. I have to initialize pci-e ASAP.(in 100~200ms from power up)

2. SBL, application, host PC need to access one big data memory block(one big structure-100MB)

3. This data memory is on DDR memory(emif)

=Question is...

1. Is this boot-up sequence correct?

2. How to declare this data memory block on specific memory address?

3. When should I declare this data memory block?

4. Should I initialize pci-e in my application again?( I guess I should)

5. Is there a better way to do this?

Please...help me~~~~~!!!

Thank you and have a nice day!!