Hi,

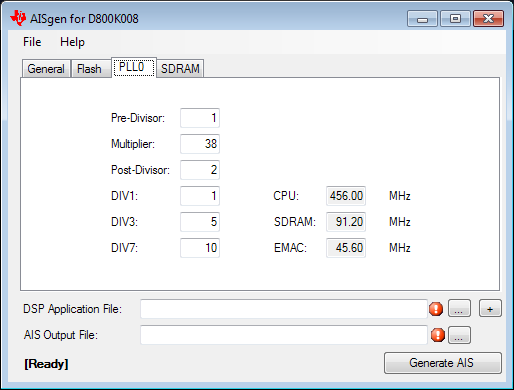

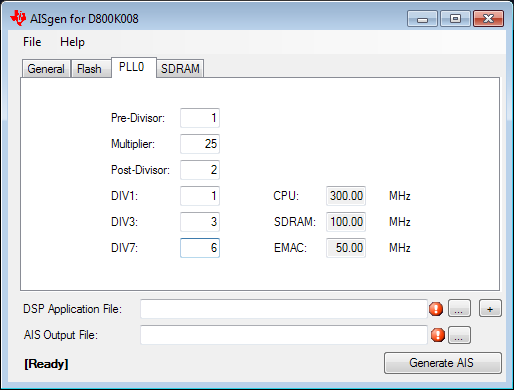

I was wondering if you could tell me which clock source sould i mark and with which frequency as well as which is the recommended frequency to set to the SDRAM and EMAC(I don't know even what EMAC Stands for) on the PLL0 and why?

Thanks in advace,

Juan