Hi, expert,

I'd like to get confirmation regarding supply ramp up (core before IO) as like this :

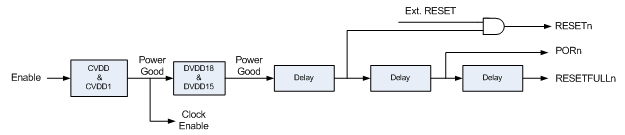

According to EVM design, it use FPGA to control ramp up sequence and reset signals by using 5 ms delay between state transition. In some E2E discusion, some design use 8 ms or 11 ms delays. But I did not find the timing specification for this in the datasheet except 100 us + 16 us delay before releasing PORn for the time of device initialization phase. Is there any special reasion to use several miliseconds delay in every state transition ?

Regard,

Sympson