Team,

this is continuation of the existing thread (linked here).

We are facing with a problem at booting. This issue was found at only one card so far, but we would like to know the background of it.

So I try to describe the problem:

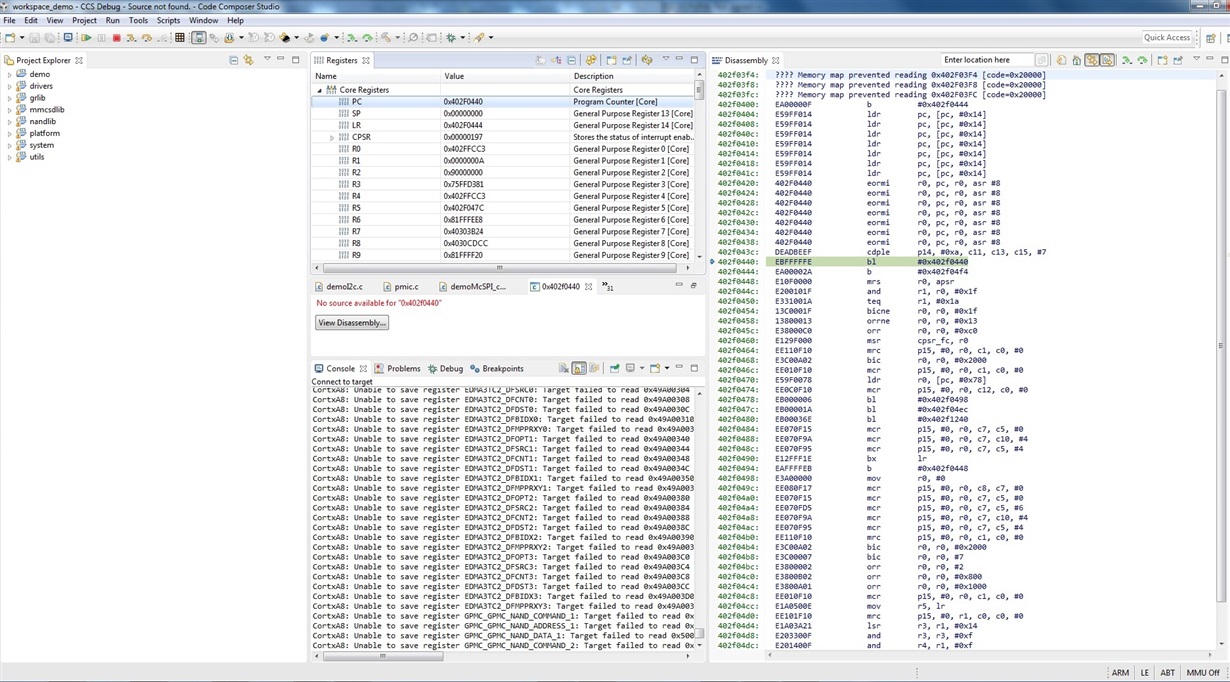

If the card is booting from the TFTP server through KSZ8463RL switch I have seen that the Program Counter is stuck at 0x402f0440 and hanging on this point (attached a picture about it below). I also attached the register values at this state.

I thought that this problem related to the DDR, but if I try to load the same (SPL and UBoot image) into serial port, the card will booting.

It seems that the problem appears only at first start, while the temperature of the card is about room temperature. The second boot is OK, if I am waiting for an hour to decrease the card temperature the problem will appear again.

I have just checked the voltages and the clocks of the Processor and the DDR and those seem to be OK, and after the reset the SYSBOOT[15:0] value is 1000 0000 0101 0000.

Can you please help solving this issue?

Thank you

TI Customer