Other Parts Discussed in Thread: CCSTUDIO, TMS320C6657, TCI6636K2H, SYSBIOS, 66AK2H12, HL5CABLE

Tool/software: TI-RTOS

Hi,

we are using your ti-rtos hyperlink example (no xDMA or Interrupt configuration) and in some HW configurations using K2H (EMV board using RTM BOC) and a couple of C6657 (EVM board only to be tested HL C6657 HL connection):

1) K2H and C6657 in internal loop works

2) C6657<-> C6657 works

3) K2H <-> C6657 not works on both K2H ports (0/1)

The test is stop when it tried to read a remote register.

I have tested some SW configurations:

1) 1 lane @ 3.125Gb/s

2) 4 lanes @ 6.25Gb/s

3) Debug/Release version

On k2h side I can see this behaviour:

Version #: 0x02010008; string HYPLNK LLD Revision: 02.01.00.08:Oct 6 2018:02:57:41

About to do system setup (PLL, PSC, and DDR)

Constructed SERDES configs: PLL=0x00000228; RX=0x0046c495; TX=0x000ccf95

system setup worked

About to set up HyperLink Peripheral

============================Hyperlink Testing Port 0

========================================== begin registers before initialization ===========

Revision register contents:

Raw = 0x4e902101

Status register contents:

Raw = 0x00003004

Link status register contents:

Raw = 0x00000000

Control register contents:

Raw = 0x00000000

Control register contents:

Raw = 0x00000000

============== end registers before initialization ===========

Hyperlink Serdes Common Init Complete

On C6657 side instead:

Version #: 0x02010006; string HYPLNK LLD Revision: 02.01.00.06:Mar 28 2017:14:26:56

About to do system setup (PLL, PSC, and DDR)

Constructed SERDES configs: PLL=0x00000064; RX=0x0046c4a5; TX=0x000ccfa5

system setup worked

About to set up HyperLink Peripheral

============================Hyperlink Testing Port 0

========================================== begin registers before initialization ===========

Revision register contents:

Raw = 0x4e901900

Status register contents:

Raw = 0x00000004

Link status register contents:

Raw = 0x00000000

Control register contents:

Raw = 0x00000000

Control register contents:

Raw = 0x00000000

============== end registers before initialization ===========

Waiting for other side to come up ( 0)

SERDES_STS (32 bits) contents: 0x03060c19; lock = 1

Waiting for other side to come up ( 1)

Waiting for other side to come up ( 2)

Waiting for other side to come up ( 3)

Waiting for other side to come up ( 4)

Waiting for other side to come up ( 5)

.....

Seems serdes configuration problem, isn't' it?

#define hyplnk_EXAMPLE_PORT 0

#define hyplnk_EXAMPLE_REFCLK_USE_PLATCFG

#define hyplnk_EXAMPLE_ALLOW_1_LANE

#define hyplnk_EXAMPLE_SERRATE_03p125

#define hyplnk_EXAMPLE_ASYNC_CLOCKS

#define hyplnk_EXAMPLE_EQ_ANALYSIS

#define hyplnk_EXAMPLE_TEST_CPU_TOKEN_EXCHANGE

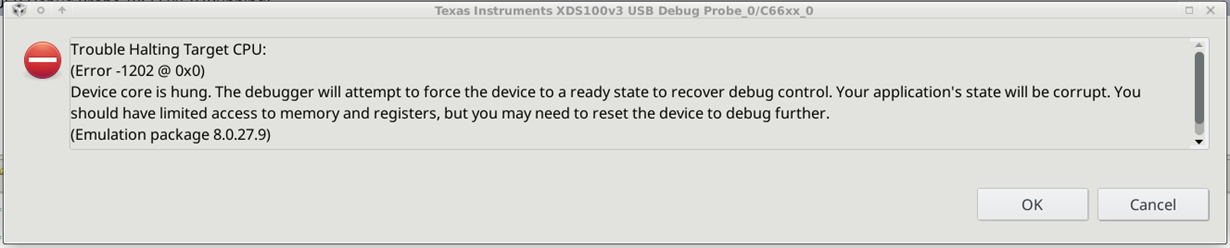

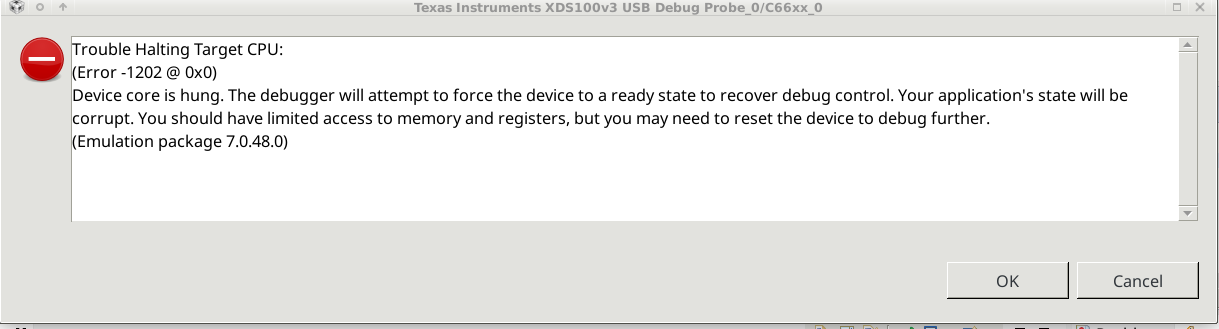

In other version (of my code) I have changed something and the lanes are working but when the code arrived at read remote register the DSP0 (CC6657) goes in crash.

On K2H Side:

00:00:20 00:00:20 hyplnkMemoryMapped.c@735: Version #: 0x02010008; string HYPLNK LLD Revision: 02.01.00.08:Oct 6

2018:02:57:41

00:00:20 00:00:00 hyplnkMemoryMapped.c@746: About to do system setup (PLL, PSC, and DDR)

00:00:20 00:00:00 hyplnkLLDIFace.c@1036: Constructed SERDES configs: PLL=0x00000228; RX=0x0046c495; TX=0x000ccf95

00:00:20 00:00:00 hyplnkMemoryMapped.c@753: system setup worked

00:00:20 00:00:00 hyplnkMemoryMapped.c@761: About to set up HyperLink Peripheral

00:00:20 00:00:00 hyplnkLLDIFace.c@1605: ============================

00:00:20 00:00:00 hyplnkLLDIFace.c@1606: Hyperlink Testing Port 0

00:00:20 00:00:00 hyplnkLLDIFace.c@1607: ============================

00:00:20 00:00:00 hyplnkLLDIFace.c@1619: ============== begin registers before initialization ===========

00:00:20 00:00:00 hyplnkLLDIFace.c@607: Revision register contents: Raw = 0x4e902101

00:00:20 00:00:00 hyplnkLLDIFace.c@656: Status register contents: Raw = 0x00003004

00:00:20 00:00:00 hyplnkLLDIFace.c@699: Link status register contents: Raw = 0x00000000

00:00:20 00:00:00 hyplnkLLDIFace.c@730: Control register contents: Raw = 0x00000000

00:00:20 00:00:00 hyplnkLLDIFace.c@752: Control register contents: Raw = 0x00000000

00:00:20 00:00:00 hyplnkLLDIFace.c@1625: ============== end registers before initialization ===========

00:00:20 00:00:00 hyplnkLLDIFace.c@534: Hyperlink Serdes Common Init Complete

00:00:21 00:00:01 hyplnkLLDIFace.c@560: Hyperlink Serdes Lane 0 Init Complete

00:00:21 00:00:00 hyplnkLLDIFace.c@1836: ============== begin registers after initialization ===========

00:00:21 00:00:00 hyplnkLLDIFace.c@656: Status register contents: Raw = 0x04400005

00:00:21 00:00:00 hyplnkLLDIFace.c@699: Link status register contents: Raw = 0xccf00cf0

00:00:21 00:00:00 hyplnkLLDIFace.c@730: Control register contents: Raw = 0x00004000

00:00:21 00:00:00 hyplnkLLDIFace.c@1840: ============== end registers after initialization ===========

00:00:21 00:00:00 hyplnkMemoryMapped.c@768: Peripheral setup worked

00:00:21 00:00:00 hyplnkLLDIFace.c@1899: Waiting 5 seconds to check link stability

00:00:26 00:00:05 hyplnkLLDIFace.c@1911: Analyzing the connection for each lane

00:00:26 00:00:00 hyplnkLLDIFace.c@1138: Precursors 1

00:00:26 00:00:00 hyplnkLLDIFace.c@1163:

00:00:26 00:00:00 hyplnkLLDIFace.c@1142: Postcursors: 19

00:00:26 00:00:00 hyplnkLLDIFace.c@1163:

00:00:26 00:00:00 hyplnkLLDIFace.c@1915: Link seems stable

00:00:26 00:00:00 hyplnkLLDIFace.c@1917: About to try to read remote registers

On C6657 side:

00:00:08 00:00:08 hyplnkMemoryMapped.c@718: Version #: 0x02010006; string HYPLNK LLD Revision: 02.01.00.06:Mar 28 2017:146

00:00:08 00:00:00 hyplnkMemoryMapped.c@728: About to do system setup (PLL, PSC, and DDR)

00:00:08 00:00:00 hyplnkLLDIFace.c@971: Constructed SERDES configs: PLL=0x00000064; RX=0x0046c495; TX=0x000cc795

00:00:08 00:00:00 hyplnkMemoryMapped.c@735: system setup worked

00:00:08 00:00:00 hyplnkMemoryMapped.c@744: About to set up HyperLink Peripheral

00:00:08 00:00:00 hyplnkLLDIFace.c@1176: ============================

00:00:08 00:00:00 hyplnkLLDIFace.c@1177: Hyperlink Testing Port 0

00:00:08 00:00:00 hyplnkLLDIFace.c@1178: ============================

00:00:08 00:00:00 hyplnkLLDIFace.c@1190: ============== begin registers before initialization ===========

00:00:08 00:00:00 hyplnkLLDIFace.c@597: Revision register contents: Raw = 0x4e901900

00:00:08 00:00:00 hyplnkLLDIFace.c@646: Status register contents: Raw = 0x00000004

00:00:08 00:00:00 hyplnkLLDIFace.c@689: Link status register contents: Raw = 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@720: Control register contents: Raw = 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@742: Control register contents: Raw = 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@1196: ============== end registers before initialization ===========

00:00:08 00:00:00 hyplnkLLDIFace.c@831: SERDES_STS (32 bits) contents: 0x05001429; lock = 1

00:00:08 00:00:00 hyplnkLLDIFace.c@781: VUSR_CFGPLL HyperLink SerDes PLL Configuration: 0x00000064

00:00:08 00:00:00 hyplnkLLDIFace.c@782: VUSR_CFGRX0 HyperLink SerDes Receive Configuration 0 : 0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@783: VUSR_CFGTX0 HyperLink SerDes Transmit Configuration 0: 0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@784: VUSR_CFGRX1 HyperLink SerDes Receive Configuration 1 : 0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@785: VUSR_CFGTX1 HyperLink SerDes Transmit Configuration 1: 0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@786: VUSR_CFGRX2 HyperLink SerDes Receive Configuration 2 : 0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@787: VUSR_CFGTX2 HyperLink SerDes Transmit Configuration 2: 0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@788: VUSR_CFGRX3 HyperLink SerDes Receive Configuration 3 : 0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@789: VUSR_CFGTX3 HyperLink SerDes Transmit Configuration 3: 0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@799: Chip Version contents: 0x0000b97a

00:00:08 00:00:00 hyplnkLLDIFace.c@801: Lane Power Management Control contents: 0x07070004

00:00:08 00:00:00 hyplnkLLDIFace.c@803: SerDes Control and Status 1 contents: 0xffff0000

00:00:08 00:00:00 hyplnkLLDIFace.c@805: SerDes Control and Status 2 contents: 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@807: SerDes Control and Status 3 contents: 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@809: SerDes Control and Status 4 contents: 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@811: Link Status contents: 0xccf00cf0

00:00:08 00:00:00 hyplnkLLDIFace.c@1404: ============== begin registers after initialization ===========

00:00:08 00:00:00 hyplnkLLDIFace.c@646: Status register contents: Raw = 0x04400005

00:00:08 00:00:00 hyplnkLLDIFace.c@689: Link status register contents: Raw = 0xccf00cf0

00:00:08 00:00:00 hyplnkLLDIFace.c@720: Control register contents: Raw = 0x00004000

00:00:08 00:00:00 hyplnkLLDIFace.c@1408: ============== end registers after initialization ===========

00:00:08 00:00:00 hyplnkLLDIFace.c@1409: Waiting 5 seconds to check link stability

00:00:13 00:00:05 hyplnkLLDIFace.c@1425: Link seems stable

00:00:13 00:00:00 hyplnkLLDIFace.c@1426: About to try to read remote registers

Could you help us?

Best regards,

Dario