Part Number: AM3352

Hello,

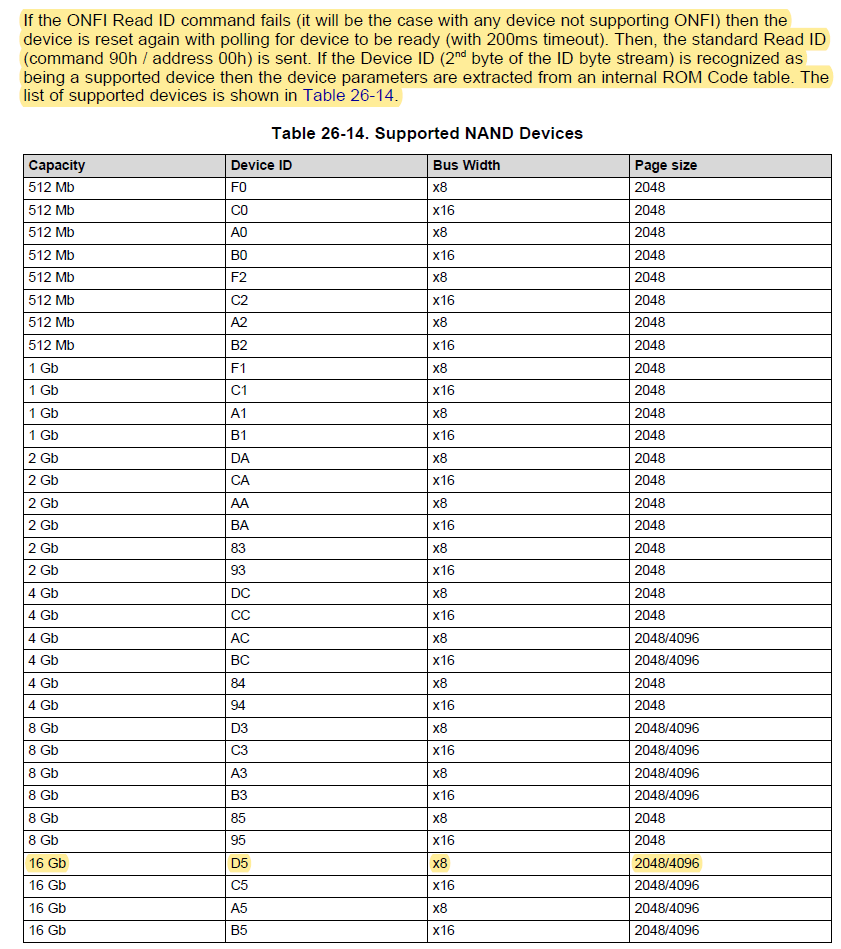

We are using am3352 with a SLC 8Gbit NAND flash. Now we need to include option for a 32Gbit NAND flash, but unfortunately we are not able to find a compatible NAND flash memry chip that fits the am335s requirements.

Main problem we are finding is pagesize, am3352 requires 2048/4096 pagesize, and available chips are 8192.

Could you please suggest compatible part numbers?

Our requirements are:

- Size: 32Gbit

- Temperature range: -40 to +85ºC

- One chip select

- 8-bit bus width

- TSOP48

- Technology: SLC preferred. MLC could be an option

Thank you for your help

Best regards

Angel