Part Number: LINUXSDK-OMAPL138

Other Parts Discussed in Thread: OMAPL138, OMAP-L138

Tool/software: Linux

Hi,

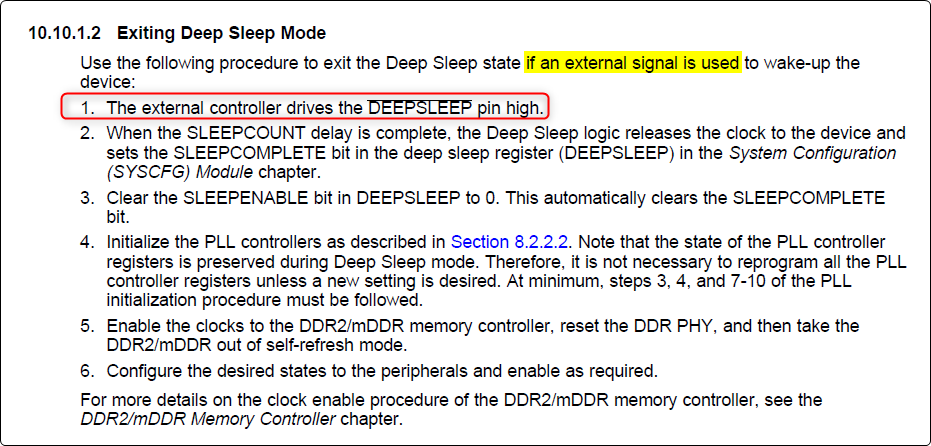

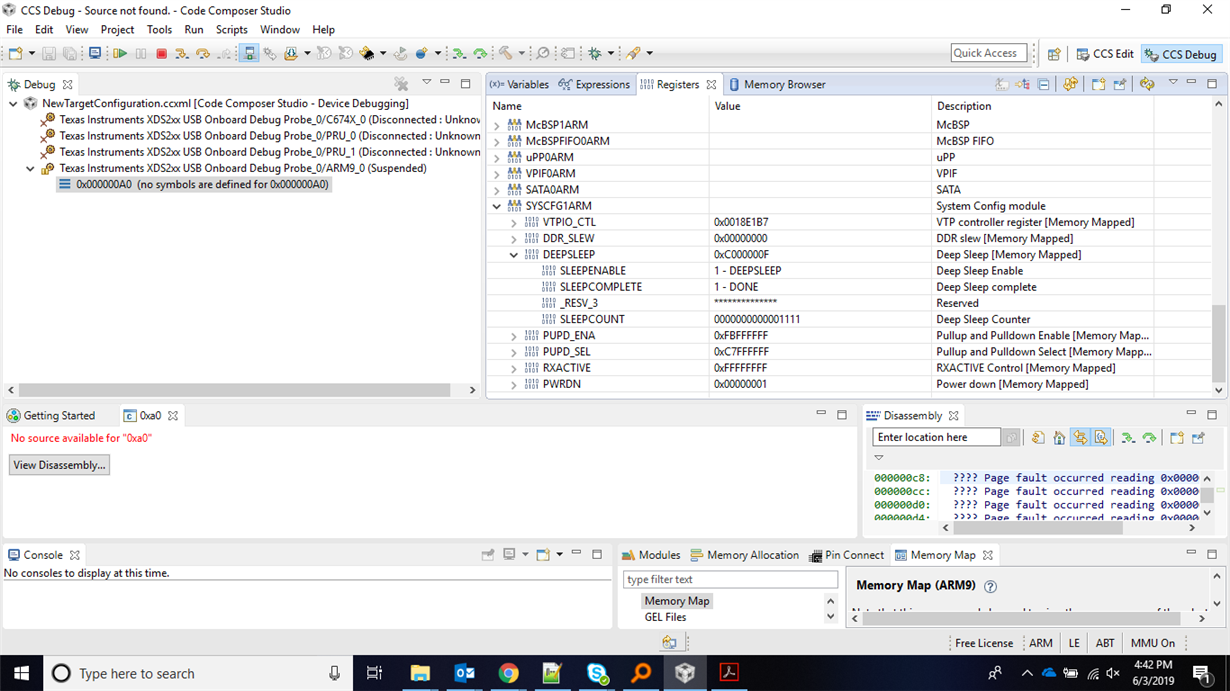

Would like to wakeup omapl138 from deepsleep mode using GP0[8].

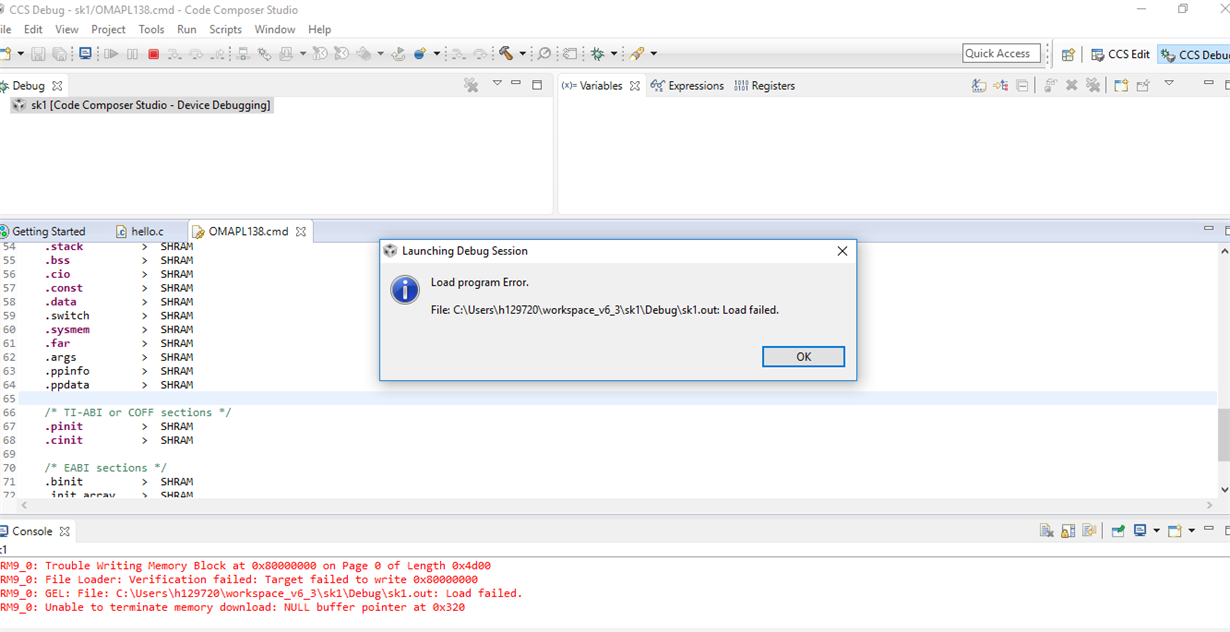

The device is entering the deepsleep mode upon doing echo mem > /sys/power/state.

Would like to wake the device up from deep sleep mode using the interrupt on GP0[8] by pulling the line low.

Please share your inputs on how to proceed on this.