Other Parts Discussed in Thread: XIO2001,

Hi

I have build the system I have described here:

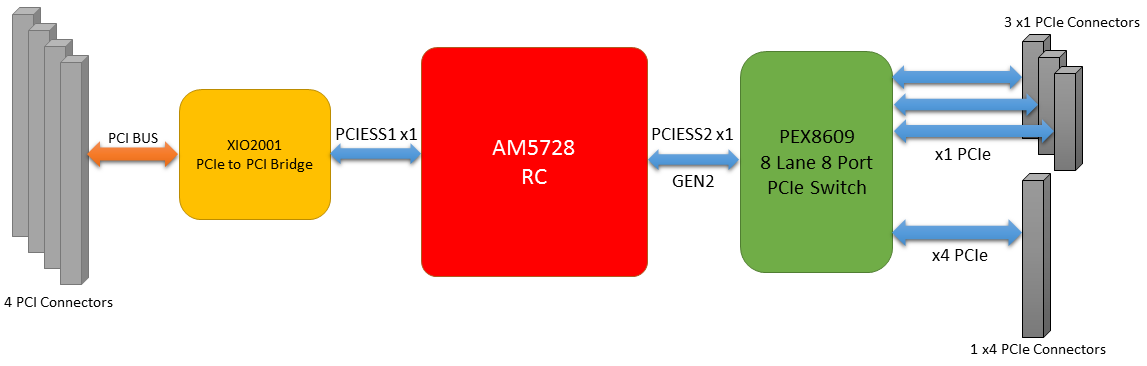

AM5728 PCIESS1 is connected to XIO2001 PCIe to PCI bridge and PCIESS2 is connected to PLX8609 PCIe switch on PCB.

Before I do any changes to PCIe sections in dts files, I have XIO2001 identified as below (SDK 06.00.00.07):

00:00.0 PCI bridge: Texas Instruments Device 8888 (rev 01) 01:00.0 PCI bridge: Texas Instruments XIO2001 PCI Express-to-PCI Bridge

Then I changed the device tree files to enable PCIESS2 as below:

In the dra7.dtsi file I have commented the //status = "disabled"; under the axi@1 section.

In the am57xx-beagle-x15-common.dtsi file I've modified related section to enable pcie2_phy and pcie2_rc as follows:

&pcie2_phy {

status = "okay";

};

&pcie1_rc {

status = "ok";

gpios = <&gpio2 2 GPIO_ACTIVE_LOW>; //PERSTn for XIO20001 on our board, was gpio2_8 for EVM

};

&pcie2_rc {

status = "ok";

gpios = <&gpio2 0 GPIO_ACTIVE_LOW>; //PERSTn for PLX8609 on our board

};

After above changes, the output of lspci is:

0000:00:00.0 PCI bridge: Texas Instruments Multicore DSP+ARM KeyStone II SOC (rev 01) 0001:00:00.0 PCI bridge: Texas Instruments Multicore DSP+ARM KeyStone II SOC (rev 01)

And I could not see XIO2001 after that. I've reversed the changes I've done, but I could not see XIO2001 again and the output is:

00:00.0 PCI bridge: Texas Instruments Multicore DSP+ARM KeyStone II SOC (rev 01)

And the output of the dmesg | grep pci when both pcie are enabled is:

root@am57xx-evm:~# dmesg | grep pci [ 0.644428] dra7-pcie 51000000.pcie: Linked as a consumer to phy-4a094000.pciephy.1 [ 0.644598] dra7-pcie 51000000.pcie: GPIO lookup for consumer (null) [ 0.644606] dra7-pcie 51000000.pcie: using device tree for GPIO lookup [ 0.644638] of_get_named_gpiod_flags: parsed 'gpios' property of node '/ocp/axi@0/pcie@51000000[0]' - status (0) [ 0.644688] dra7-pcie 51000000.pcie: WA for Errata i870 not applied [ 0.644784] dra7-pcie 51000000.pcie: host bridge /ocp/axi@0/pcie@51000000 ranges: [ 0.644826] dra7-pcie 51000000.pcie: IO 0x20003000..0x20012fff -> 0x00000000 [ 0.644856] dra7-pcie 51000000.pcie: MEM 0x20013000..0x2fffffff -> 0x20013000 [ 1.645148] dra7-pcie 51000000.pcie: Phy link never came up [ 1.645281] dra7-pcie 51000000.pcie: PCI host bridge to bus 0000:00 [ 1.645296] pci_bus 0000:00: root bus resource [bus 00-ff] [ 1.645309] pci_bus 0000:00: root bus resource [io 0x0000-0xffff] [ 1.645320] pci_bus 0000:00: root bus resource [mem 0x20013000-0x2fffffff] [ 1.645356] pci 0000:00:00.0: [104c:8888] type 01 class 0x060400 [ 1.645389] pci 0000:00:00.0: reg 0x10: [mem 0x00000000-0x000fffff 64bit] [ 1.645450] pci 0000:00:00.0: supports D1 [ 1.645458] pci 0000:00:00.0: PME# supported from D0 D1 D3hot [ 1.656451] pci 0000:00:00.0: BAR 0: assigned [mem 0x20100000-0x201fffff 64bit] [ 1.656472] pci 0000:00:00.0: PCI bridge to [bus 01-ff] [ 1.656811] pcieport 0000:00:00.0: Signaling PME with IRQ 172 [ 1.656942] pcieport 0000:00:00.0: AER enabled with IRQ 172 [ 1.657222] dra7-pcie 51800000.pcie: Linked as a consumer to phy-4a095000.pciephy.2 [ 1.657332] dra7-pcie 51800000.pcie: GPIO lookup for consumer (null) [ 1.657339] dra7-pcie 51800000.pcie: using device tree for GPIO lookup [ 1.657370] of_get_named_gpiod_flags: parsed 'gpios' property of node '/ocp/axi@1/pcie@51800000[0]' - status (0) [ 1.657399] dra7-pcie 51800000.pcie: WA for Errata i870 not applied [ 1.657487] dra7-pcie 51800000.pcie: host bridge /ocp/axi@1/pcie@51800000 ranges: [ 1.657528] dra7-pcie 51800000.pcie: IO 0x30003000..0x30012fff -> 0x00000000 [ 1.657556] dra7-pcie 51800000.pcie: MEM 0x30013000..0x3fffffff -> 0x30013000 [ 2.657849] dra7-pcie 51800000.pcie: Phy link never came up [ 2.657975] dra7-pcie 51800000.pcie: PCI host bridge to bus 0001:00 [ 2.657989] pci_bus 0001:00: root bus resource [bus 00-ff] [ 2.658003] pci_bus 0001:00: root bus resource [io 0x10000-0x1ffff] (bus address [0x0000-0xffff]) [ 2.658015] pci_bus 0001:00: root bus resource [mem 0x30013000-0x3fffffff] [ 2.658047] pci 0001:00:00.0: [104c:8888] type 01 class 0x060400 [ 2.658077] pci 0001:00:00.0: reg 0x10: [mem 0x00000000-0x000fffff 64bit] [ 2.658136] pci 0001:00:00.0: supports D1 [ 2.658143] pci 0001:00:00.0: PME# supported from D0 D1 D3hot [ 2.668942] pci 0001:00:00.0: BAR 0: assigned [mem 0x30100000-0x301fffff 64bit] [ 2.668962] pci 0001:00:00.0: PCI bridge to [bus 01-ff] [ 2.669257] pcieport 0001:00:00.0: Signaling PME with IRQ 174 [ 2.669387] pcieport 0001:00:00.0: AER enabled with IRQ 174

My question is at least how to see XIO2001 and PLX8609 switch on lspci ?

I've checked all the related threads and it seems some other guys dealt with it but it is not clear how it could be done.

e2e.ti.com/.../764228

e2e.ti.com/.../758389

e2e.ti.com/.../1799986

e2e.ti.com/.../595948

e2e.ti.com/.../2476292

e2e.ti.com/.../597740