Other Parts Discussed in Thread: SYSBIOS

Hallo,

I have a bare metal motion application on C66_1 and C66_2. The processing performance is outstanding (a bunch of complex calculations are done in less than 1.3 µs).

But I noticed breaks within the processing flow. When I searched for the reason I found an unexpected long interrupt latency on C66. So I write a very simple test:

main

{

while( 1 )

{

set pin high

set pin low

}

}

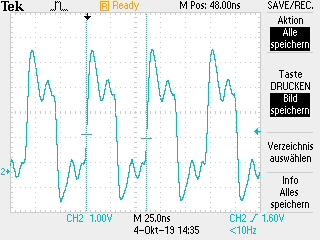

On scope I can see the pin toggling with a pulse with of 50 ns. Now I implemented period timer with interrupt like this:

Init_Timer4( 1 ms );

// Register Timer4 interrupts on to INTC

{

const uint32_t XBarInstSysTimer = CSL_XBAR_INST_DSP1_IRQ_32;

const uint32_t SysTimerIntC66 = 32;

CSL_xbarIrqConfigure( CSL_XBAR_IRQ_CPU_ID_DSP1, XBarInstSysTimer, CSL_XBAR_TIMER4_IRQ );

Intc_IntRegister( SysTimerIntC66, SysTimer_Handler, NULL);

Intc_IntPrioritySet( SysTimerIntC66, 1, 0);

Intc_SystemEnable( SysTimerIntC66 );

}

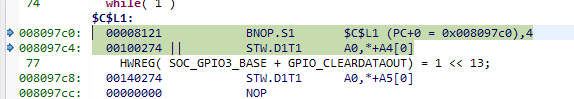

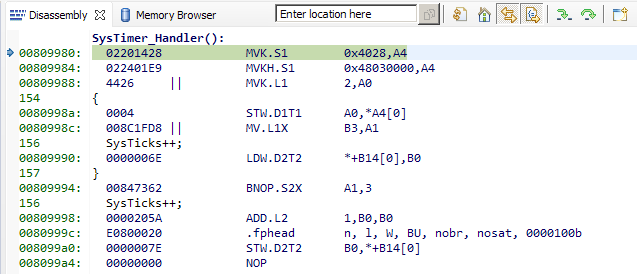

void SysTimer_Handler( void *handle )

{

HWREG( SOC_TIMER4_BASE + TIMER_IRQSTATUS) = TIMER_IRQSTATUS_OVF_IT_FLAG_MASK;

SysTicks++;

}

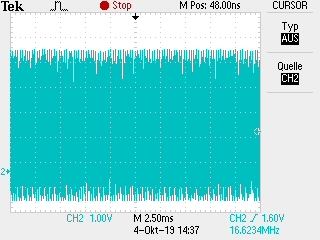

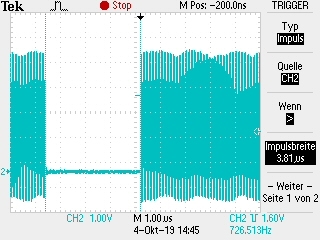

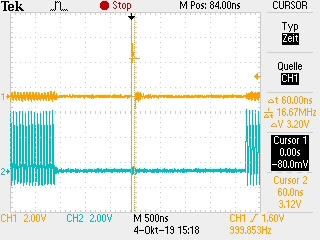

On scope I still see my pin toggeling with 20 MHz, but each one millisecond there is a large gap.

This is the time where the C66 is hanging out in the timer interrupt.

According to the documentation I expected this gap shall 300 to 500 ns.

But the time where the main loop is inactive is nearly 4 microseconds long!

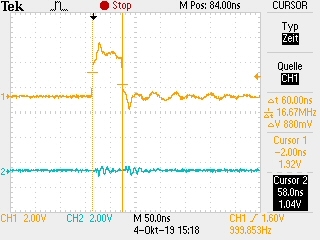

I also measured the time of execution of SysTimer_Handler(), but this is very short (below 100 ns).

It seems the C66 has an interrupt latency of nearly 4 µs instead of some 100 nano seconds.

I could not believe it and double checked my measurements. But I can not found any fault.

How long is the interrupt latency of the C66?

What is going wrong?

Please note:

C66 is running directly from internal SRAM (not from OCMC and not from DDR3). Clock is 600 MHz.

The really good processing performance proof it is not a memory access or clock problem.

What should be done to reduce the interrupt latency significat?

Regards Dirk