Hi experts,

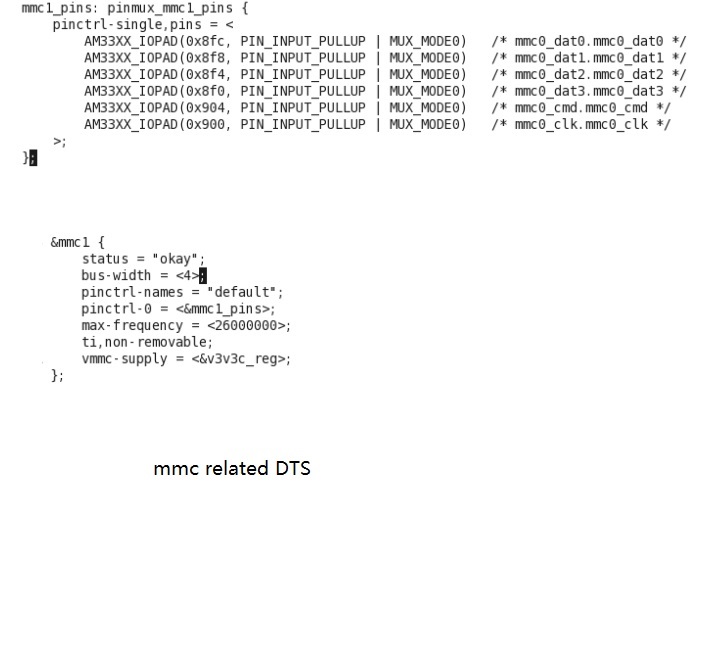

I have one board designed with am335x and emmc, while I got the error as shown below. So I made some measurement to check the timing between clock and CMD line. It looks like in low speed, the response from device is driven in the falling edge of clock, while in high speed mode, the response from device is driven in the rising edge.

1) Is the waveform for high speed mode correct? I checked am335x datasheet, page 221, the setup and hold time should be 4.1ns/3.76ns separately.

2) If it's not correct, is there any timing parameter I can set to fix this problem?

For low speed (about 400kHz), for the response from emmc, the rising edge of clock is in the middle of CMD line, copied below.

During transferring data, the emmc will be in high speed mode, I copied a response (command 13) below.

Thanks

Chris