Other Parts Discussed in Thread: AM5718

processor_sdk_rtos_am57xx_3_01_00_06

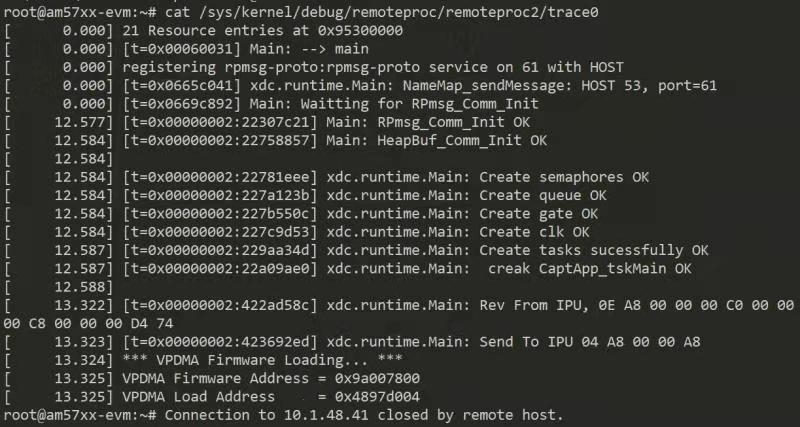

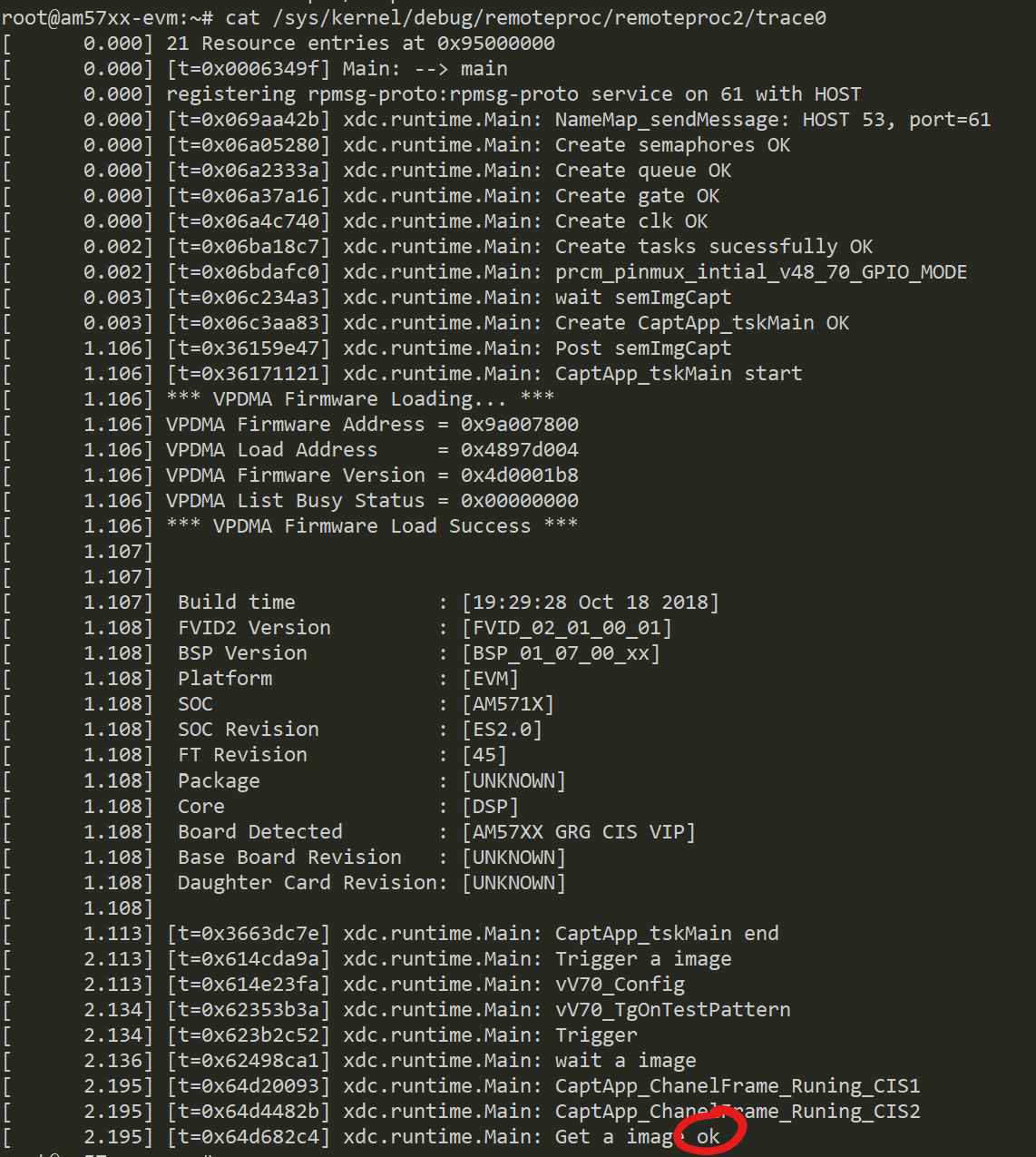

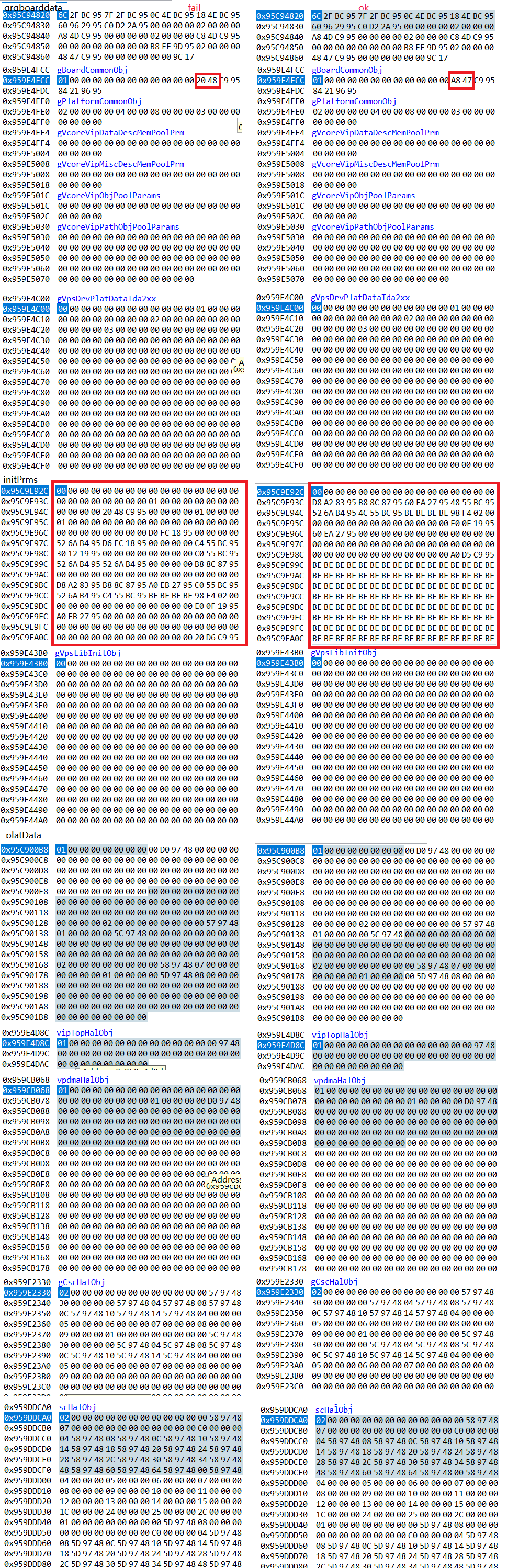

Assign 64Mbyte space for DSP, but actually can only use 14Mbyte, if assigned size over 14Mbyte, program hangin VPDMA firmeware loading.

VPS library modified in attached source code,DSP project based on IPC demo, not sure where is the issue, please help to analysis.

source code size over 20Mbyte, I zipped into 2 files attached.

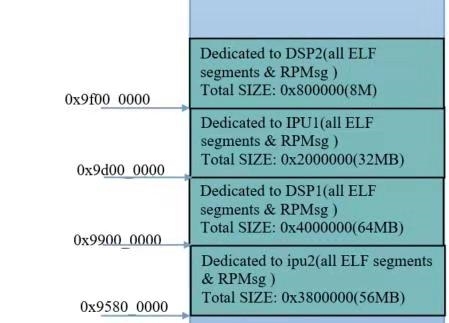

Address space assign as below,DSP1 space in 0x99000000~0x9d000000,it is 64M.

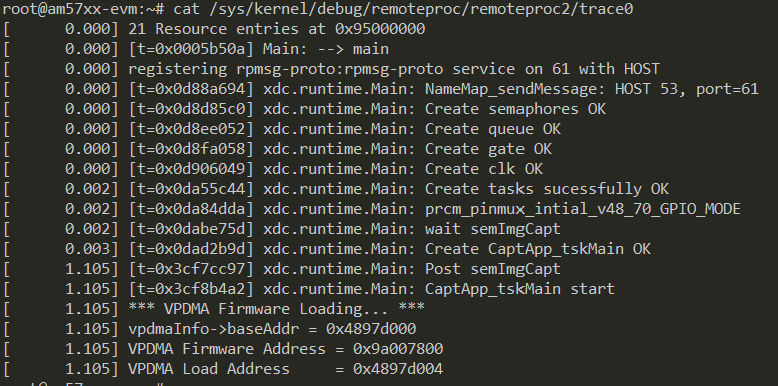

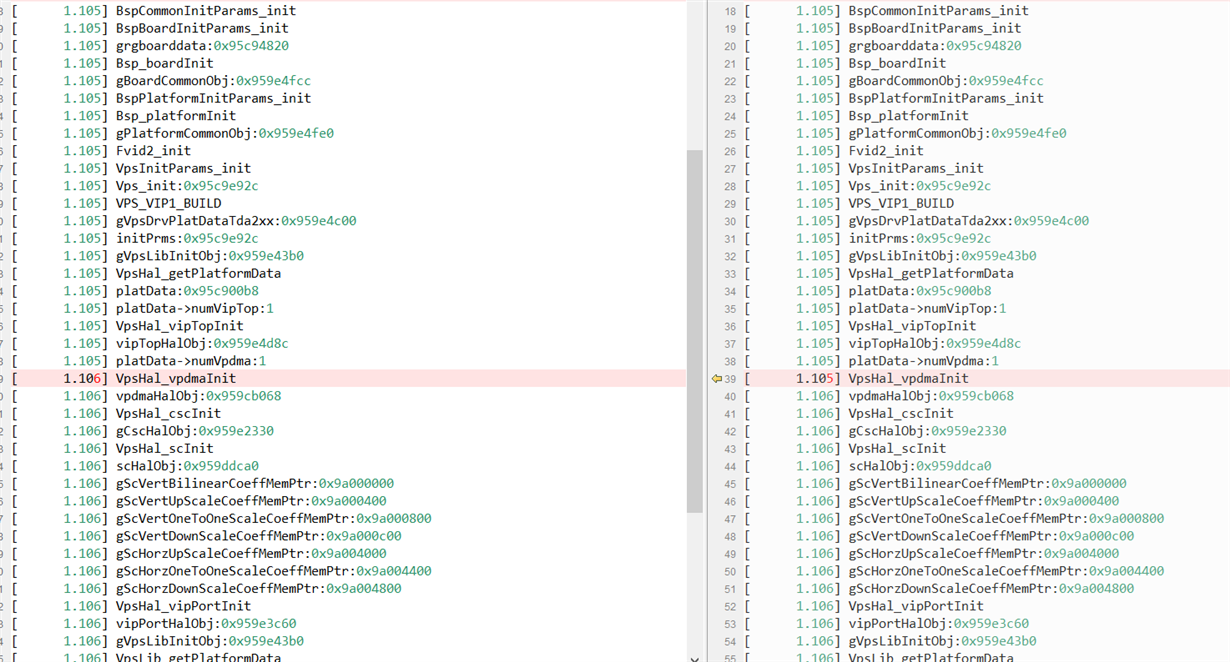

Program hangs in VPDMA Firmware loading

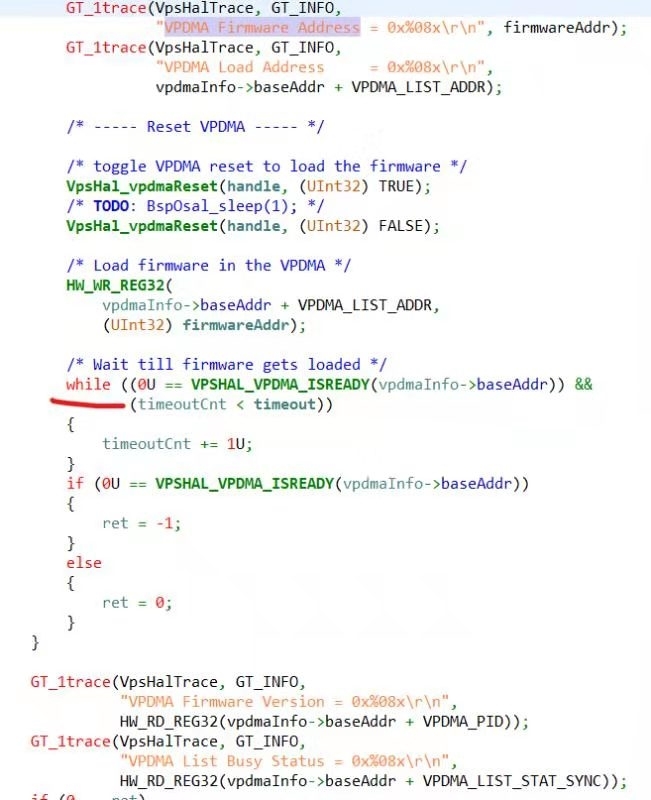

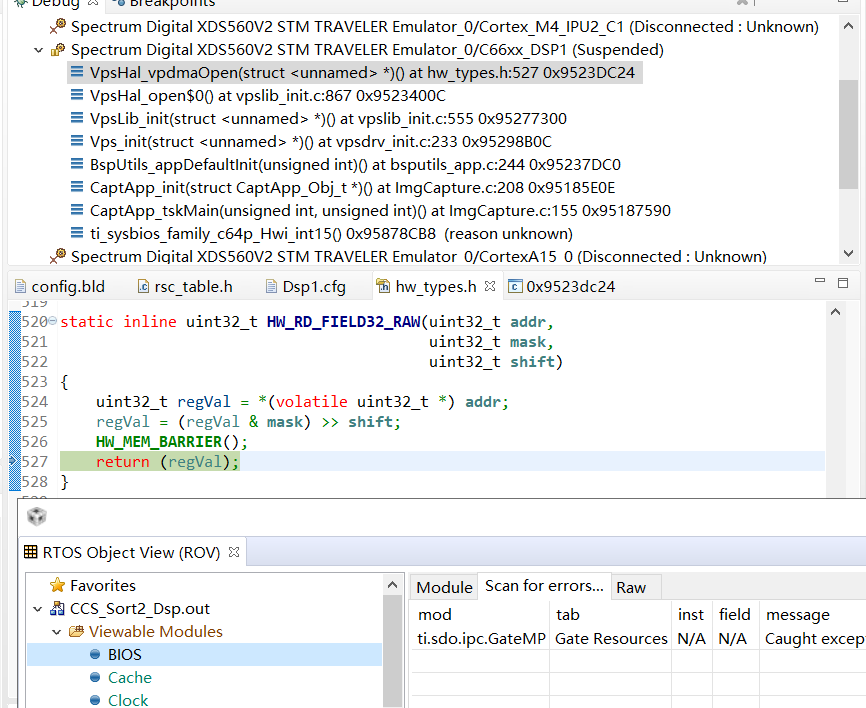

Figured out hanging on the line of while of vps/src/vpslib/hal/src/vpshal_vpdma.c in below snapshot: