Part Number: AM5728

I am using the mcspiLoopbackApp example. I then wrap a loop around the

SPI_transfer(gSpiHandle, &transaction);

The loop sends a SPI_transfer around 4000-5000 times before the following error occurs.

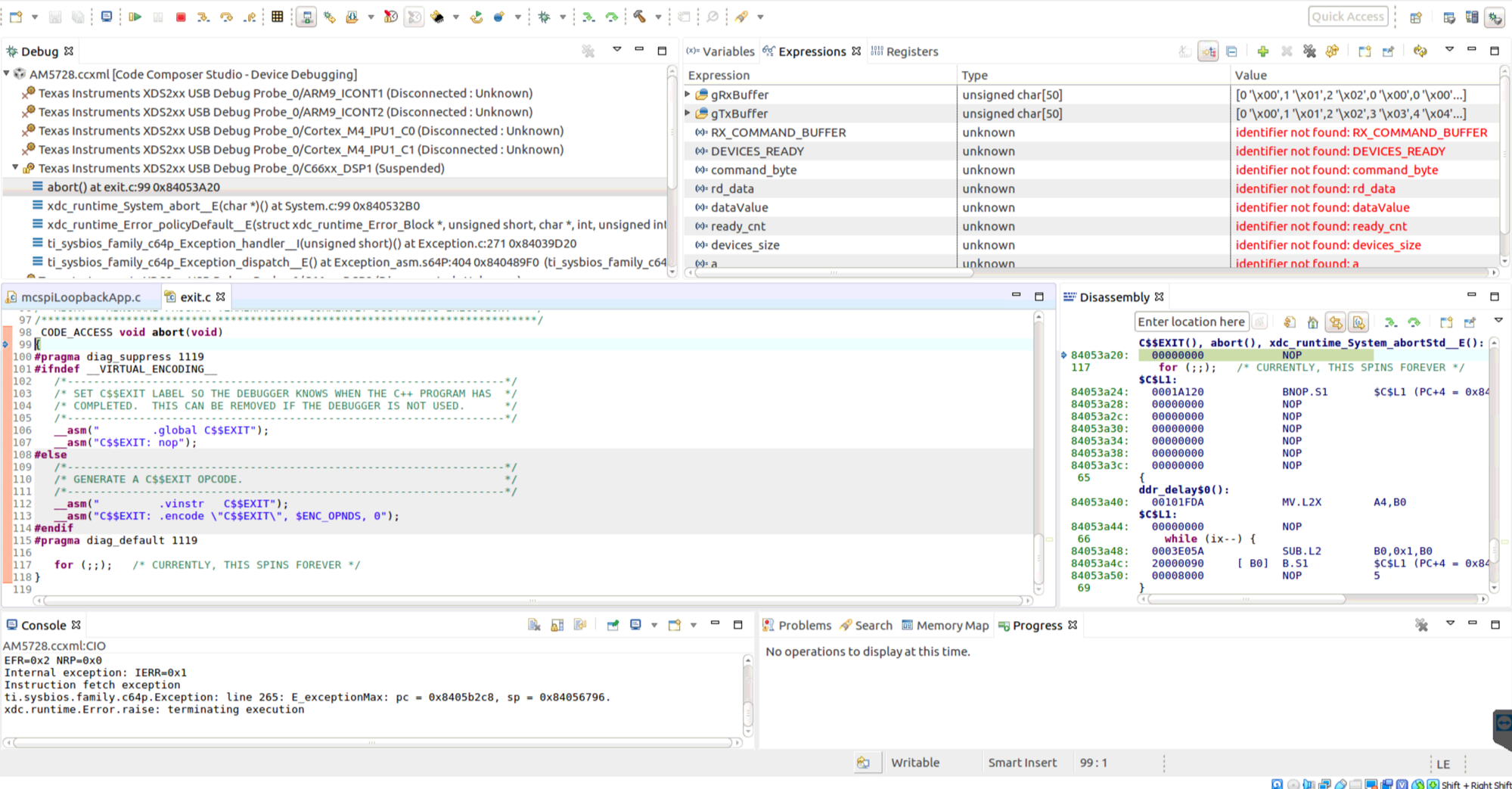

Exception at 0x0 EFR=0x2 NRP=0x0 Internal exception: IERR=0x1 Instruction fetch exception ti.sysbios.family.c64p.Exception: line 265: E_exceptionMax: pc = 0x8405b2c8, sp = 0x84056796. xdc.runtime.Error.raise: terminating execution

This seems like a memory error. I have attached my code so you can reproduce this issue.