How I can configure vsdk links for provide frames for 4x channels from ISS to VIP on the fly? Or maybe have you example for vps drivers? It's need for convert 422I to 420SP without access to DDR and save bandwith DDR from excess RD/WR

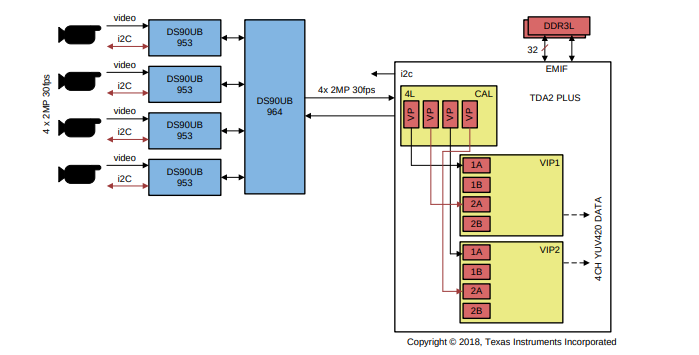

as in the example 2.1.4 CAL to VIP 4 Channel Capture (SPRACE3A–April 2018)