Dear champs,

My customer is trying to make RGMII2 working in the U-boot but could not succeed to get response when they tried to ping.

Could you please check my customer's configuration in the dts and board.c?

HW is custom board and MII1 was connected to mac0 and RGMII2 was connected to mac1.

SW is Linux Processor SDK 6.1.

In dts,

&mac {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&cpsw_default>;

pinctrl-1 = <&cpsw_sleep>;

dual_emac;

active_slave = <1>;

status = "okay";

};

&davinci_mdio {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&davinci_mdio_default>;

pinctrl-1 = <&davinci_mdio_sleep>;

status = "okay";

};

&cpsw_emac0 {

phy_id = <&davinci_mdio>, <8>;

phy-mode = "mii-txid";

dual_emac_res_vlan = <1>;

};

&cpsw_emac1 {

phy_id = <&davinci_mdio>, <0>;

phy-mode = "rgmii-txid";

dual_emac_res_vlan = <2>;

};

cpsw_default: cpsw_default {

pinctrl-single,pins = <

/* Slave 1 */

0x40 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a0.rgmii2_tctl */

0x44 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a1.rgmii2_rctl */

0x48 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a2.rgmii2_td3 */

0x4c (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a3.rgmii2_td2 */

0x50 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a4.rgmii2_td1 */

0x54 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a5.rgmii2_td0 */

0x58 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a6.rgmii2_tclk */

0x5c (PIN_INPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a7.rgmii2_rclk */

0x60 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a8.rgmii2_rd3 */

0x64 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a9.rgmii2_rd2 */

0x68 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a10.rgmii2_rd1 */

0x6c (PIN_INPUT_PULLDOWN | MUX_MODE2) /* conf_gpmc_a11.rgmii2_rd0 */

>;

};

in board.c

/* CPSW platdata */

#if !CONFIG_IS_ENABLED(OF_CONTROL)

struct cpsw_slave_data slave_data[] = {

{

.slave_reg_ofs = CPSW_SLAVE0_OFFSET,

.sliver_reg_ofs = CPSW_SLIVER0_OFFSET,

.phy_addr = 8,

},

{

.slave_reg_ofs = CPSW_SLAVE1_OFFSET,

.sliver_reg_ofs = CPSW_SLIVER1_OFFSET,

.phy_addr = 0,

},

};

struct cpsw_platform_data am335_eth_data = {

.cpsw_base = CPSW_BASE,

.version = CPSW_CTRL_VERSION_2,

.bd_ram_ofs = 0x2000,

.ale_reg_ofs = 0xd00,

.cpdma_reg_ofs = 0x800,

.mdio_div = 0xff,

.host_port_reg_ofs = 0x108,

.channels = 8,

.slaves = 2,

.slave_data = slave_data,

.ale_entries = 1024,

.bd_ram_ofs = 0x2000,

.mac_control = 0x20,

.active_slave = 0,

.mdio_base = 0x4a101000,

.gmii_sel = 0x44e10650,

.phy_sel_compat = "ti,am3352-cpsw-phy-sel",

.syscon_addr = 0x44e10630,

.macid_sel_compat = "cpsw,am33xx",

};

struct eth_pdata cpsw_pdata = {

.iobase = 0x4a100000,

.phy_interface = 0,

.priv_pdata = &am335_eth_data,

};

U_BOOT_DEVICE(am335x_eth) = {

.name = "eth_cpsw",

.platdata = &cpsw_pdata,

};

#endif

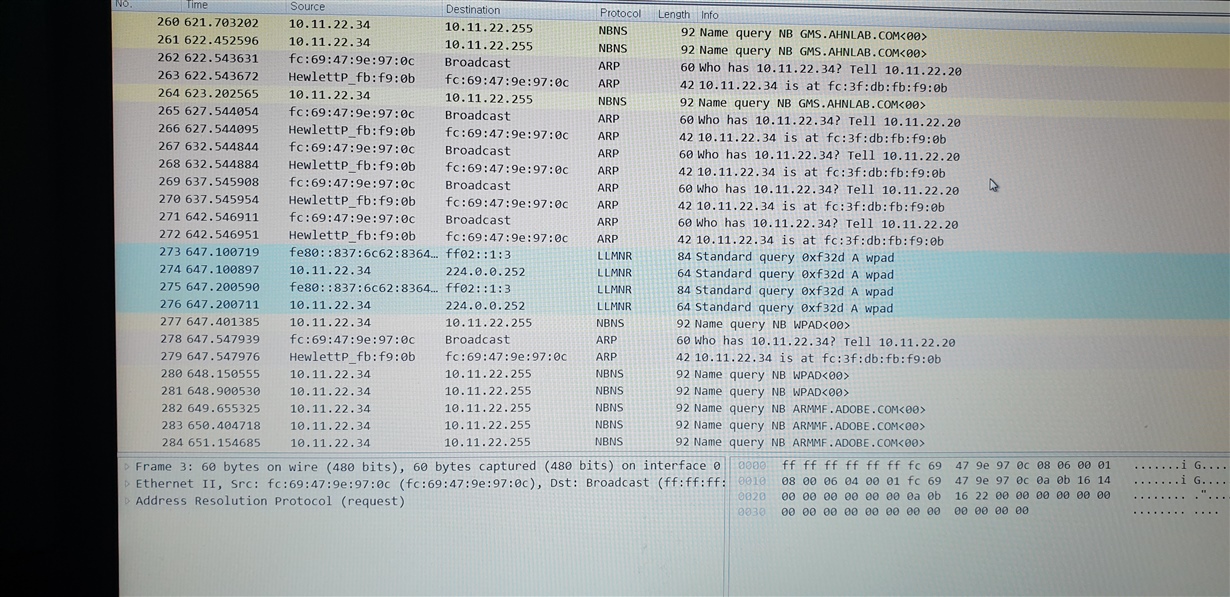

When I checked cpsw_ALE control register, it was all '0' as below, but I think it should be set to '1' in the 'vlan_aware' bit field at least because they should use 'dual mac' mode. is my observation right?

| CONTROL | 0x00000000 |

And also, could you please let me know what should be done to make working rgmii2 in the u-boot?

When they tried to ping, there was no response.

And, I'm curious why 'RNDIS ready' was printed in the console. they just make few modification for their custom board from the u-boot source of PSDK.

Thanks and Best Regards,

SI.