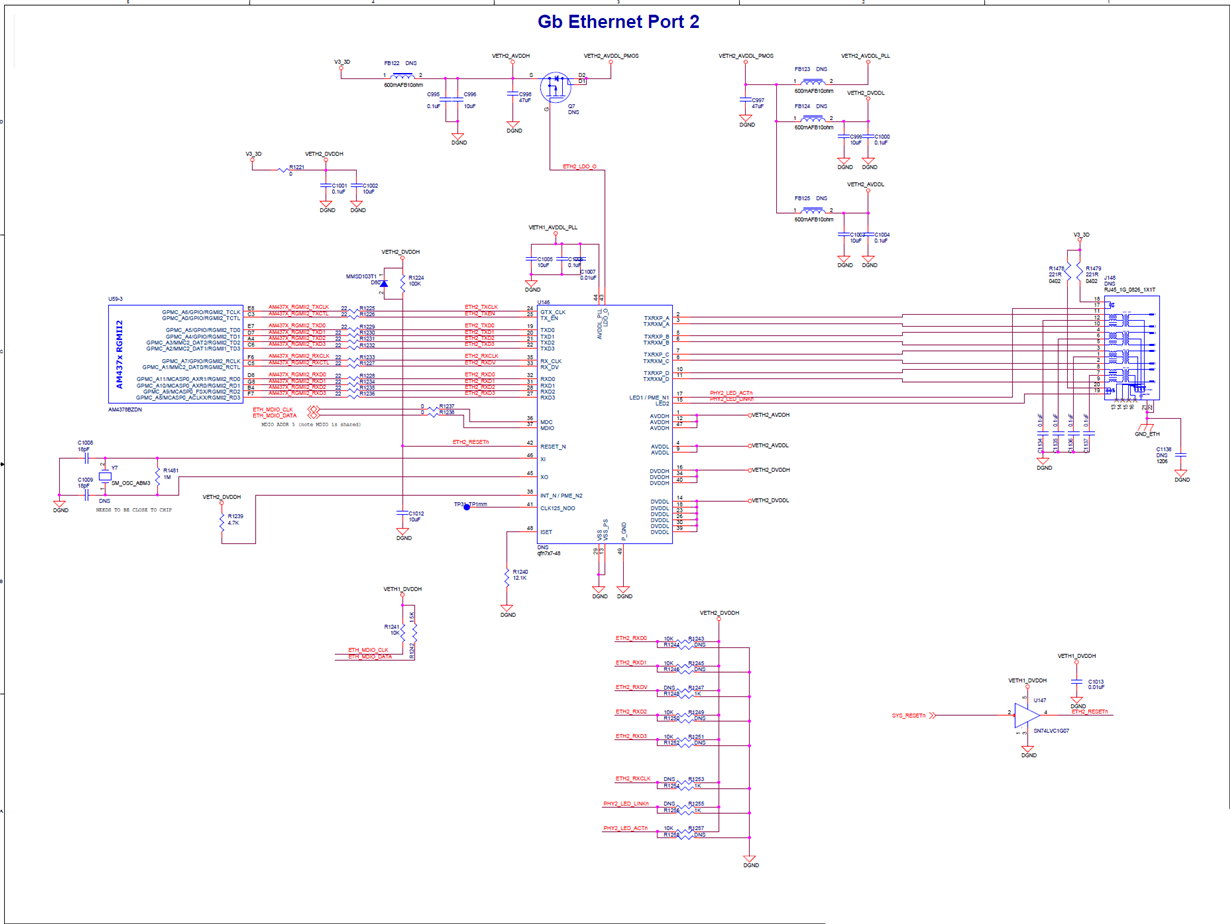

We have a custom board based heavily off of am437x-sk-evm. The first ethernet port is working fine, but plugging in the second ethernet port causes a reboot.

A few more datapoints:

* Booting via ethernet works as long as second port is not plugged in. If it is plugged in then the board repeatedly restarts in the Boot ROM

* The 2nd ethernet port is connected identically as the am437x-sk-evm except for ETH2_INTn--it is not used and not connected to the processor.

* Plugging in the second ethernet port will cause a reset up until the point Linux loads the USB and Network drivers. From that point forward it will not trigger a reboot

* The 2nd ethernet port is not required to be usable in u-boot

Does anyone have any suggestions? I have tried both configuring the pins of RGMII2 and also setting them as GPIOs. Neither seems to work