Other Parts Discussed in Thread: SYSBIOS

Hi Champs:

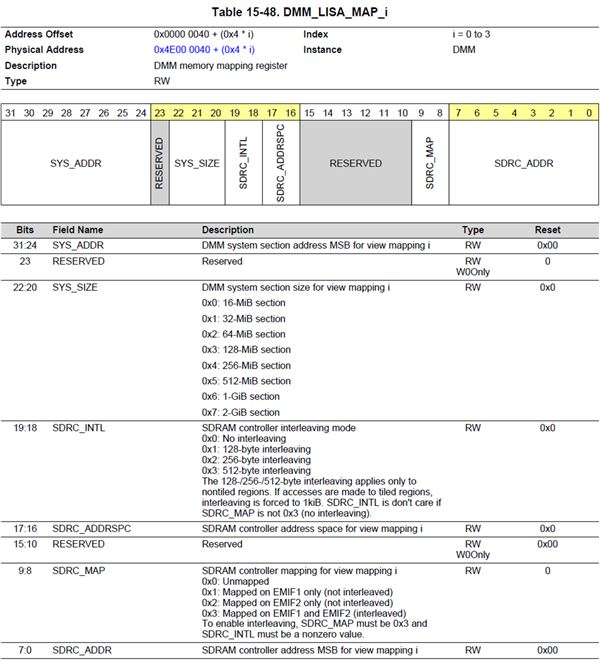

Customer is making the TIDL SSD for 720P, he is able to change the EMIF from 512MB to 512X2MB (Dual EMIF) as expected.

Now, he is asking if we are able to enlarge the SR1 ?

and can he modify with DUAL_EMIF with 1GB_512MB?

Please comment, thanks.

BR Rio