Part Number: TDA4VM

Hi TI Support Team

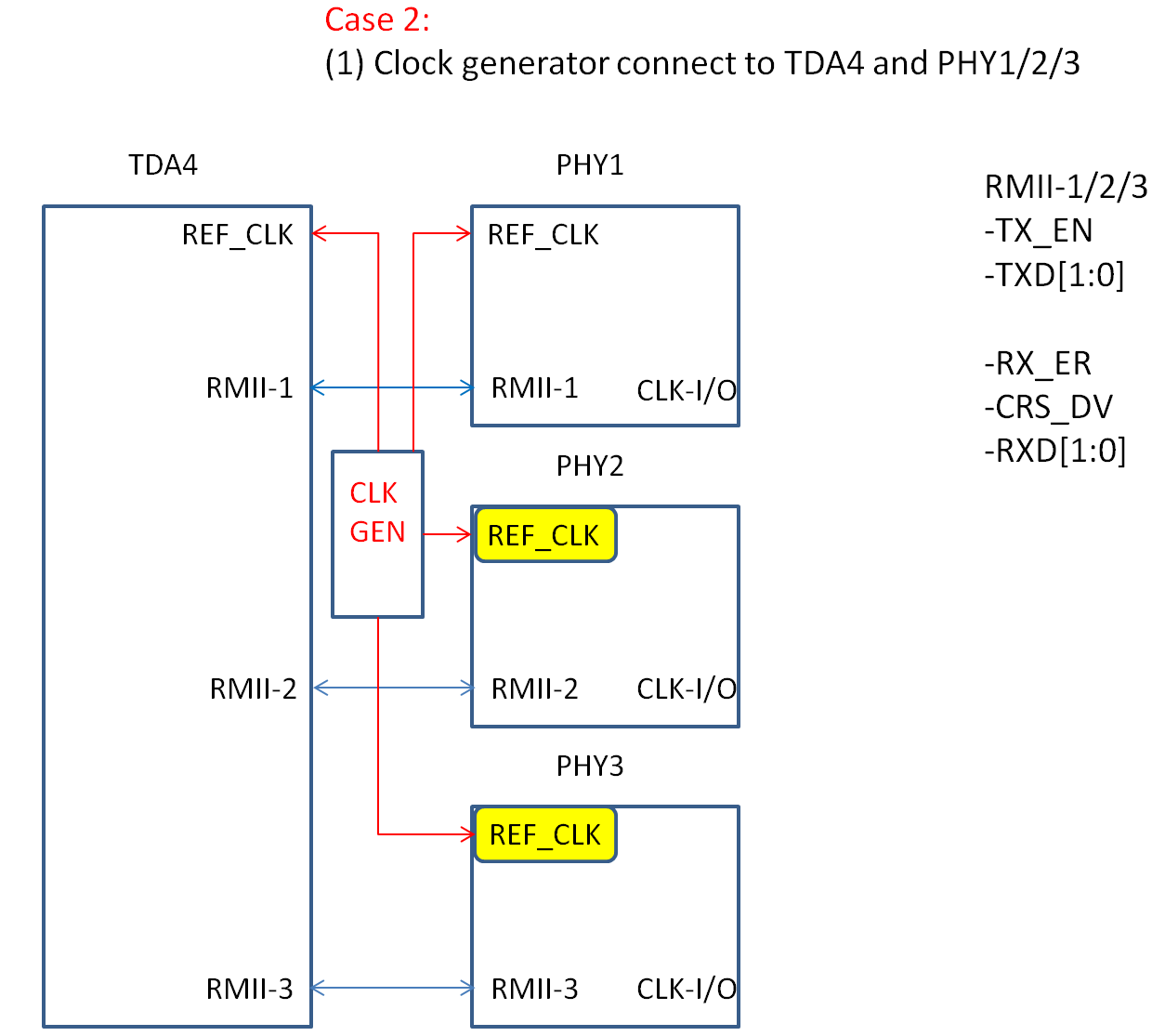

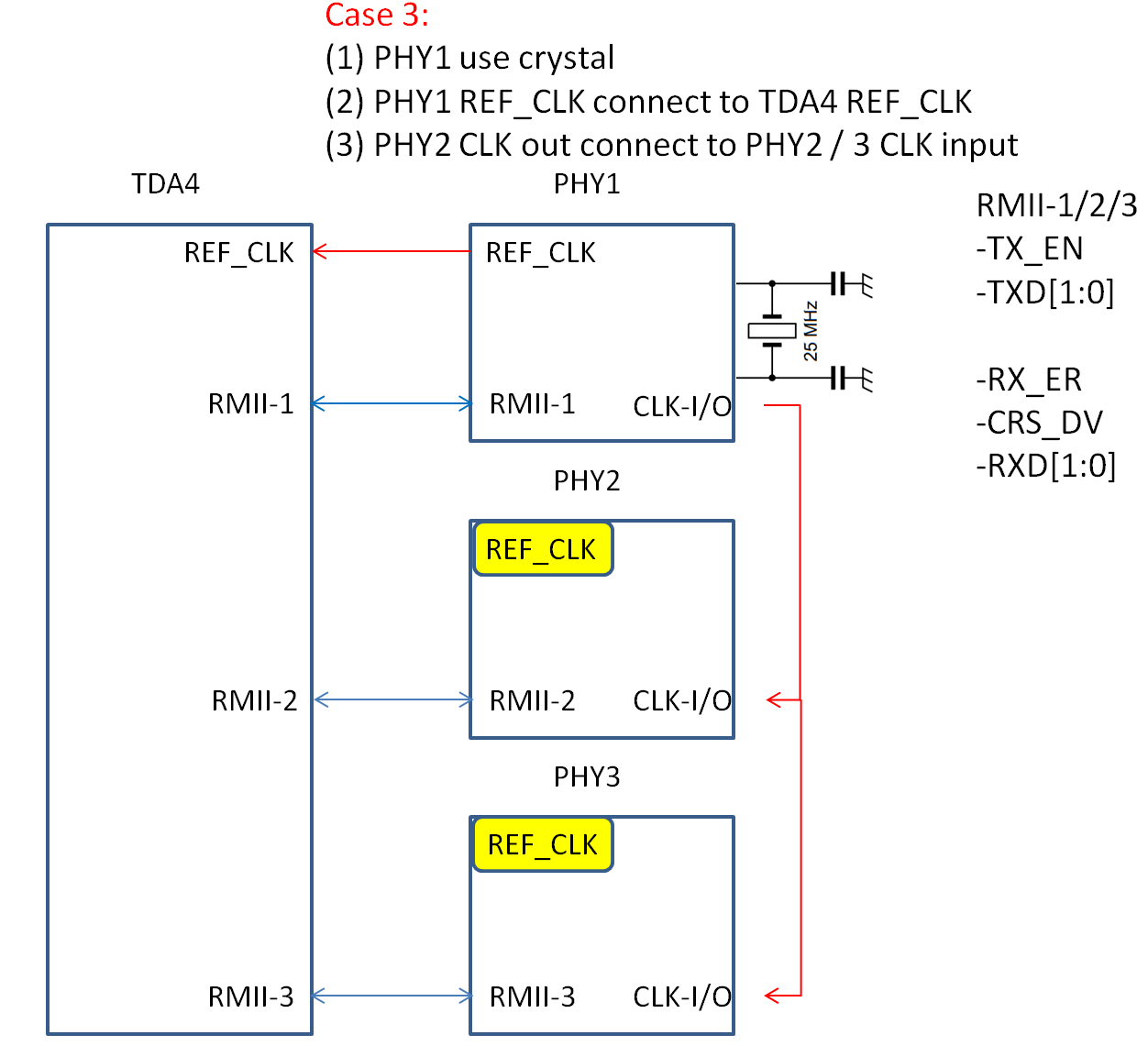

We want to use 3 PHY (RMII) connect to TDA4 CPSW9 (Main) Ethernet domain.

As the TDA4 only have one REF_CLK pin for all CPSW9 RMII interface. So I want to double check with you about the REF_CLK connection concept. If every PHY REF_CLK need connect to TDA4 REF_CLK.

Please check the below use case 1 / 2 / 3. I want to know if they can working or not ?

Thanks

Yutai