Part Number: AM5716

Other Parts Discussed in Thread: TPS51200

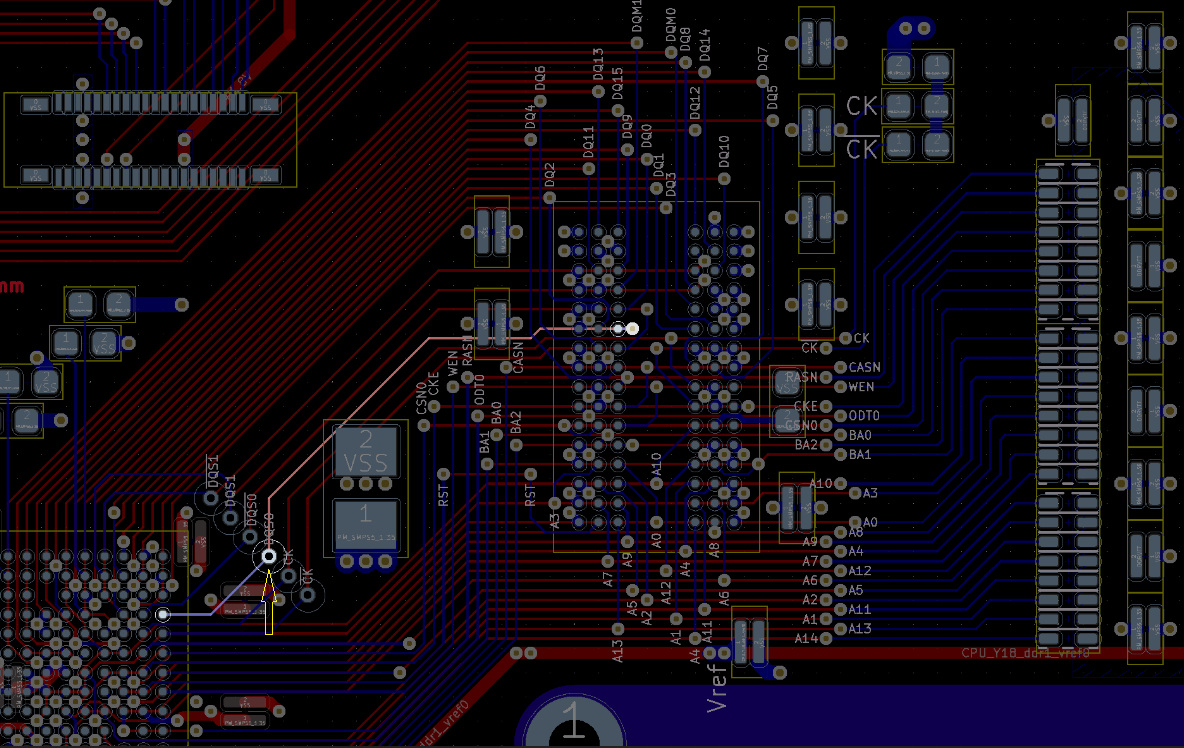

I'm working on a new design using an AM5716 and a single 4Gb DDR3L part #AS4C256M16D3LC-12BCN. The data is not correct when viewing in the memory browser and I see traces on the data lines that looks incorrect. While I am sure the SI of this design is not ideal, I think there may be something much bigger that I am still missing. Perhaps you can spot it!

The write errors follow somewhat of a pattern. I also get more or less sporadic read errors when viewing it real time during continuous reads.

Fill with 0x00000000

Fill with 0xFFFFFFFF

Fill with 0xAAAAAAAA

One of the biggest red flags that I might have found is that the data lines seem to not be pulled or terminated at all, perhaps. The rising edge is quick, but the falling edge is very slow over milliseconds.

The schematic is shown below:

I've attached the EMIF spreadsheet, as well as my custom GEL files. I am operating the DDR at 400MHz. I can get other traces or any other information that might be useful. Thank-you for your help!