Hi

■Question

How can I boot with a memory map that has a program in the range of 64bit addresses?

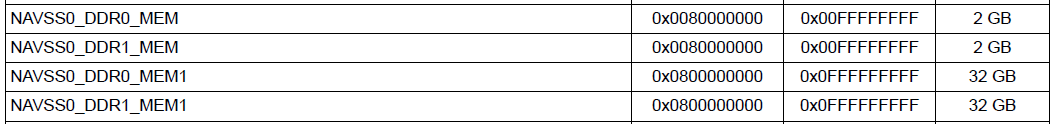

■Memory map of TDA4VM (DDR)

■MMU settings of BOOT phase (initial value)

The CMMU at startup only covers the range 0x00 00000000 - 0x03 FFFFFFFF

→Sections in the range 0x08 00000000 - 0x0F FFFFFFFF should not be accessible at startup

→If placed in this section, it is expected to freeze during initialization of the .bss and .data sections

Thanks and Best regards,

HaTa