Hi,

I have set HDMI to Vout1 / DP1 according to the following link, but the clock(pclk) is always about 600 MHz, How to modify it(148.5MHz)?

Looking forward to your reply, thanks a lot!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

I have set HDMI to Vout1 / DP1 according to the following link, but the clock(pclk) is always about 600 MHz, How to modify it(148.5MHz)?

Looking forward to your reply, thanks a lot!

Could you please share the output files? i want to see how much is the difference.

Also i am assuming that this is output directly from DSS in YUV422 format, there is no other conversion.

Regards,

Brijesh

OK,

This is the original image of yuyv (1920 * 1080)

This is the picture of yuv420-nv12 (1920*1080)received by another chip (they always think that the picture of YUV422 sent out from tda4 is incorrect. They used an oscilloscope to check the 16 data lines of tda4),as follows:

Looking for your reply!

Hi,

Are you sure that output is in YUV422 ie BT1120 format? The output values looks completely different.

Regards,

Brijesh

Hi,

The value of the DSS0_VP_CONFIG register is: 0x03200000

The value of the DSS0_VID_ATTRIBUTES register is: 0x00280AFD

So the VP output has been configured to bt.1120 mode, and the pixel format is 0x3e: yuv2.

How to continue the investigation next, ORZ........

Looking forward to your reply, thanks a lot!

Hi,

We have checked the background color and the output with the black background color is matching with the expected output.

Now we have connected actual video pipeline. so can you please share register dump of the video pipeline that you are using? I think some configuration is not correct in the video pipeline?

Regards,

Brijesh

Hi,

The value of the register is as follows:

| Registers | Value | |

| DSS0_VID_ATTRIBUTES | 0x04A20020 | 0x00080A7D |

| DSS0_VID_ATTRIBUTES2 | 0x04A20024 | 0x3C000000 |

| DSS0_VID_LUMAKEY | 0x04A202B8 | 0x00000000 |

| DSS0_VID_CROP | 0x04A202C0 | 0x00000000 |

| DSS0_VID_PIPE_GO | 0x04A202C8 | 0x00000000 |

| DSS0_VID_CSC_COEF0 | 0x04A20040 | 0x015F0100 |

| DSS0_VID_CSC_COEF1 | 0x04A20044 | 0x01000000 |

| DSS0_VID_CSC_COEF2 | 0x04A20048 | 0x07AA074D |

| DSS0_VID_CSC_COEF3 | 0x04A2004C | 0x00000100 |

| DSS0_VID_CSC_COEF4 | 0x04A20050 | 0x000001BB |

| DSS0_VID_CSC_COEF5 | 0x04A20054 | 0xC0000000 |

| DSS0_VID_CSC_COEF6 | 0x04A20058 | 0x00000000 |

| DSS0_VID_CSC_COEF7 | 0x04A2023C | 0x00000000 |

Looking forward to your reply, thanks a lot!

Hi,

I see in the register dump the pipeline is enabled, and data format is set to YUV422, but resizer is not somehow enabled. Atleast horizontal resizer should be enabled in order to convert yuv422 to yuv444. Without this, output color will not be correct. Can you try manually enabling it?

Also do you have any other pipeline connected to this display and getting blended with this pipeline? Then also the output values can change..

Regards,

Brijesh

Hi,

I want to configure all DSS modules of bypass, do bit exact output. The configuration is as follows:

·DSS0_OVR_CONFIG.TCKLCDENABLE = 0; Disable the transparency color key for the LCD

·DSS0_VP_CONFIG.CPR = 0; Color Phase Rotation Disabled

·DSS0_VP_CONFIG.TDMENABLE = 0; TDM disabled

·DSS0_VP_CONFIG. DATALINES = 0x1; 16-bit output aligned on the LSB of the pixel data interface

·DSS0_VID2. DSS0_VID_ATTRIBUTES.FORMAT = 0x3; RGB16-565

·DSS0_VID2. DSS0_VID_ATTRIBUTES.RESIZEENABLE = 0x0; Disable both horizontal and vertical resize processing

·DSS0_VID2. DSS0_VID_SIZE.SIZEX == DSS0_VID2.DSS0_VID_PICTURE_SIZE.MEMSIZEX

·DSS0_VID2. DSS0_VID_SIZE.SIZEY == DSS0_VID2.DSS0_VID_PICTURE_SIZE.MEMSIZEY

Can the above configuration bypass all DSS modules, do bit exat output?

Btw,

I happened to find that when the Y、U and V components of YUV422 are all 0x96(150), the transmission is correct. So I checked the 0-255, when Y、U and V components are the same and all are 81-174, the transmission is completely correct, and other ranges have changed. What is the reason?

Looking forward to your reply!

Hi,

The input YUV422 data will get converted first into YUV444 and then to RGB. So there is conversion involved in the display pipeline, which can change the component values. The lsb bits of the pixel, at max 3, can change the values.

Do you see only lsb bits changing?

Regards,

Brijesh

Hi, thank you for your reply!

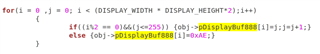

I changed the array of YUV422-YUYV in the application program, as follows (the first 256 y components are changed to 0-256, and the other Y, U, V components are filled with 0xae):

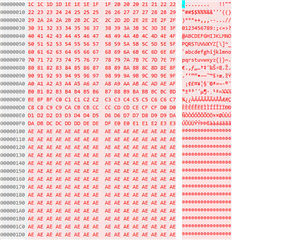

The YUV-NV12 after receiving is as follows:

Looking forward to your reply!

Hi,

One question, are you trying to enable BT1120 output from DSS? If yes, then no need to set data lines to 16bit and format to RGB565, in below two configuration.

·DSS0_VP_CONFIG. DATALINES = 0x1; 16-bit output aligned on the LSB of the pixel data interface

·DSS0_VID2. DSS0_VID_ATTRIBUTES.FORMAT = 0x3; RGB16-565

Regards,

Brijesh

Hi hui wang,

Thanks for the update.

Please close the thread if you think your question is answered.

Regards,

Brijesh