Part Number: TDA4VM

Hi,

I have set HDMI to Vout1 / DP1 according to the following link, but the clock(pclk) is always about 600 MHz, How to modify it(148.5MHz)?

Looking forward to your reply, thanks a lot!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TDA4VM

Hi,

I have set HDMI to Vout1 / DP1 according to the following link, but the clock(pclk) is always about 600 MHz, How to modify it(148.5MHz)?

Looking forward to your reply, thanks a lot!

Hi,

Which video port output are you connected to vout1? Accordingly, we can use/change pixel clock for that video port output.

Regards,

Brijesh

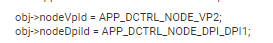

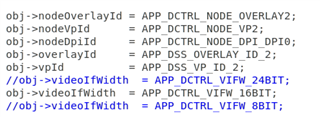

Hi, I use VP2 connected to vout1,as following

For HDMI output, vision apps connects VP2 output to vout0 (DP0) and pixel clock is 148.5MHz. When I switch to Vout1 / DP1 (use VP2), the clock is wrong ,is not 148.5MHz.

How can I change it?

Hi,

But have you changed the pinmux accordingly and measuring clock on correct pin? Because since you are using same VP2 output, PLL will remain same.

Regards,

Brijesh

Hi,

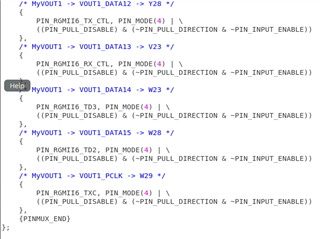

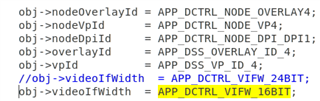

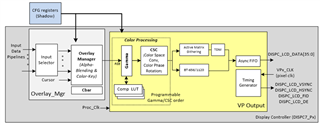

I'm sure it's changed. My amendment is as follows:

1、pinmux(vision_apps/utils/misc/src/app_pinmux.c)

2、appDssDefaultInit (vision_apps/utils/dss/src/app_dss_defaults.c)

3、According to the above content, the clock will be abnormal (It is different from the following (vision_apps/utils/dss/include/app_dctrl.h) configuration, but vout0/dp0 is ok).

so, what's wrong with it?

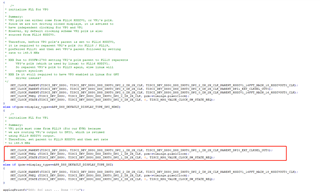

I wonder if the following (vision_apps/utils/dss/src/app_dss_j721e.c) should be revised as well. If so, can you tell me how to do it.

Look forward to your reply!

Hi Wang,

Can you please check which VP is connected to DPI1 output port in COMMON_DISPC_CONNECTIONS register at the offset 0x04A000E4?

Also please check if DPI is enabled in the VP2_Control register at offset 0x04AA0004?

Could you please take dump of all COMMON registers from offset 0x04A00000 (100 registers) and all VP registers for all VP?

Regards,

Brijesh

Hi Hui Wang,

Unfortunately, no, it does not support reading multiple register.

Regards,

Brijesh

Hi,

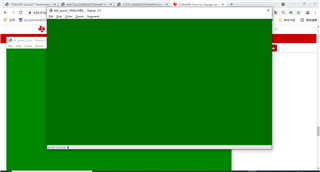

I can read the value in the register with devmem2 tool. Now I can transfer the picture with bt1120, but the result is wrong,as follow

Original picture(YUV422):

Picture after transmission:

The value of the DSS0_VP_CONFIG register is:0x03200000

Look forward to your reply!

Hi hui wang,

No, WB path is not supported.

since you are using bt1120 output, sync polarity does not mater. can you check pixel clock edge polarity? I think by default it is set to active low. can you try inverting it in app_dss_defaults.c file?

Regards,

Brijesh

Hi,

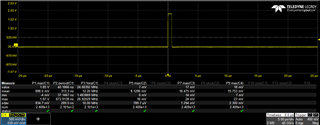

I tried two ways, no change, as follow

The value of the DSS0_VP_POL_FREQ register is:0x000040000 or 0x00000000

But, I made the following attempts

· Enable or Disable Color Space Conversion RGB to YUV

·Color Space Conversion full or limit range setting

The results are as follows:

·Original picture:

·Enable CSC and full range setting

·Enable CSC and limit range setting

·Disable CSC

How to locate? Where are the problems?

look forward to your reply!

Hi,

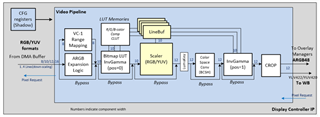

Since you are using BT1120 output, which is YUV422 output over 16bit interface, CSC is must. It must be enabled to convert overlay RGB output to YUV422 format. This is already taken care by driver.

Also please check what is the expected input sequence for chroma data in your receiver. I thing DSS outputs U first, then V on chroma 8bit output.

Regards,

Brijesh

Hi,

I've tried to change the endian (big or little), more mistakes after changing.

But, I found a phenomenon,as follow:

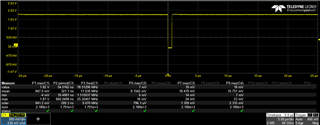

·At the beginning of the system, I didn't run any programs, but the data lines of PCLK and DATA had signals

What's the matter? Will it affect the communication of bt1120?

look forward to your reply!

Hi,

If you are using vision apps, the display would be started at the init time and it would start displaying background color.

The actual display will start only when you run some usecase/OpenVX Graph. Until than, it will continue displaying background color. So it are seeing toggle on pixel clock and data lines due to this, it should be fine.

Regards,

Brijesh

Hi,

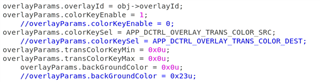

I found the reason, Is the difference between the following two parameters:

·Source transparency color key

·Destination transparency color key

Thank you very much for your answers!

This issue will not be closed for the moment, because I will debug Display2 and display3 next. I'll need your answer then!

Hi hui wang,

Depending on the source of the transparency selected, this feature can make color in source as transparent. Please refer to TRM for more details. TRM explains it with the example.

Do you see greenish picture because of this feature?

Regards,

Brijesh

Hi,

I tried two configurations, and the second one worked

1、

overlayParams.colorKeyEnable = 0;

overlayParams.colorKeySel = APP_DCTRL_OVERLAY_TRANS_COLOR_DEST;

2、

overlayParams.colorKeyEnable = 0;

overlayParams.colorKeySel = APP_DCTRL_OVERLAY_TRANS_COLOR_SRC;

According to the second configuration method, then the green background of the picture is gone.

Hi,

Strange, but the color keying is disabled by setting colorkeyenable parameter to 0. So it should not have affected. Can you check in the DSS register if color keying is enabled?

Regards,

Brijesh

ok, please close the thread, if you think your question is answered.

Regards,

Brijesh

Hi,

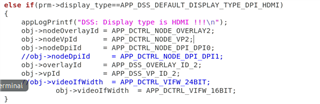

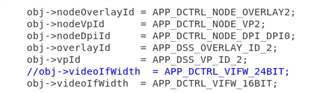

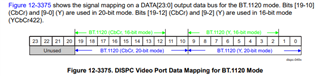

For other reasons, I need to modify videoport. When I switched to VP4, Vout1 was always problematic. The following is my debugging record:

1、app_dss_defaults.c

2、app_dss_j721e.c

3、The value of the associated register

·DSS0_VP_CONFIG(04AE0000): 03200000

·DSS0_COMMON_DISPC_CONNECTIONS(04A000E4): 00000080

·DSS0_VP_POL_FREQ(04AE004C): 00000000

·DSS0_VP_CONTROL(04AE0004): 00000141

Because bt1120 will send background information when the system starts, I measured the data lines of two kinds of Vout, found a phenomenon ,as follow:

·data0, data4 and data15 in VOUT0 have data signals, but data2 and data6 in VOUT1 have data signals.

Is it the above phenomenon that causes Vout1 to be wrong all the time? If so, how to solve it? If not, how to locate the cause of the problem?

Looking forward to your reply!

Hi wang,

VP and vout are two different things. vout is output signals, whereas VP will generate timings. So changing VP will most likely not change the behavior.

We need to see why there are incorrect colors in the output.

When you change output to vout1, can you probe all 16 data lines to confirm they are toggling? In addition, can you check pinmux values of vout1 to confirm it is set for vout1 output?

Regards,

Brijesh

Hi,

Thank you for your reply!

I use the pinmux configured by the ti-pinmux tool, I think there should be no mistakes.

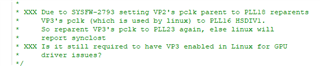

I changed not only the videoport, but also the clock. The clk settings for VP2 in vision_apps are as follows:

My changes as following, Can the following configuration be used as the CLK of VP4?

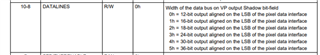

And what do the notes in the document mean? as following:

Looking forward to your reply!

Hi wang,

but these changes are specific to clock, and i guess you are able to setup clock correctly.

I still have doubt on the pinmux setting. Can you please verify the pinmux settings when usecase is running?

Regards,

Brijesh

Hi,

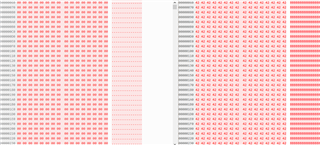

The result of previous debugging is still problematic, though there is no difference in the naked eye (a picture is bright and a picture is dark). We compared the hexadecimal system and found that the two images (All 0 yuv images) are completely different, as follows:

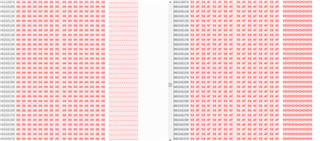

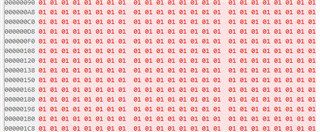

Y component(The original picture is all 0, and the tda4 transmitter is 42):

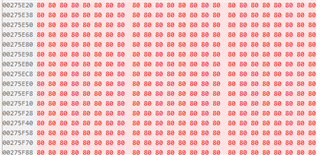

UV component(The original picture is full 0, and the tda4 transmitter becomes 594F):

The contrast between the two images is as follows(a picture is bright and a picture is dark):

What has been checked is as follows:

1、pinmux:all right

2、gamma correction:disable

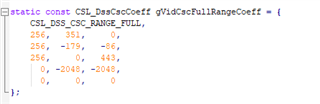

3、color space conversion full range setting: full range setted

look forward to your reply!

Hi hui wang,

Is below thread also for the same topic?

can we please continue discussion on single thread?

Regards,

Brijesh

Hi,thank you for your reply!

Yes, It's the same project.

OK, I will close that thread.

After the above phenomenon (the hexadecimal format of the two yuv images is different), I did the following checks:

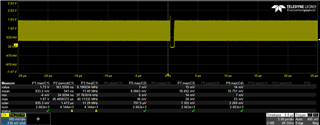

1、Each data line is measured with an oscilloscope,all 0 YUV image transmission should not appear the following waveform:

2、Checked pinmux setting (padconfig of vout0), as following:

·The value of each register is 0x0001000a

So I think pinmux is right

3、gamma correction、color space conversion full range setting

·gamma correction:disable

·color space conversion full range setting: full range setted

4、

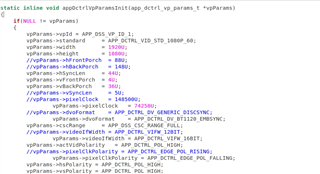

I modified it in file:ti-processor-sdk-rtos-j721e-evm-07_02_00_06/vision_apps/utils/dss/src/app_dss_defaults.c.

I tried 12bit, 16bit, 24bit, but the received YUV image did not change (including the converted hexadecimal file),So I don't think this is the place to change bt.1120 mode (16 bit mode or 20 bit mode). Is my understanding right? Where can I change bt.1120 mode?

Finally, what other settings will change the data flow and how to check?

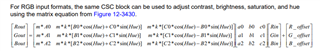

Hi wang hui,

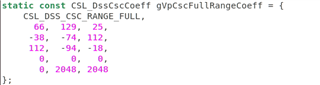

For BT66/BT1120 output, input YUV data first gets converted into RGB and then RGB gets converted into YUV back. These two CSC blocks should be matching to match the output. Could you please check if they are matching?

This light/dark output cannot be because of pinmux, gamma correction, 16bit output interface.

Lets check each module in the pipeline to confirm they are matching with the input frame's requirement.

Regards,

Brijesh

Hi,

It is inside the driver, not in vision apps.

YUV2RGB is set up in ti-processor-sdk-rtos-j721e-evm-07_01_00_11\pdk_jacinto_07_01_00_45\packages\ti\csl\src\ip\dss\V4\priv\csl_dssVideoPipe.c and RGB2YUV, it is set in ti-processor-sdk-rtos-j721e-evm-07_01_00_11\pdk_jacinto_07_01_00_45\packages\ti\csl\src\ip\dss\V4\priv\csl_dssVideoPort.c

Rgds,

Brijesh

Btw, are you using limited range CSC output or full range? If limited range, can you try with the full range output?

what is your input data format? Is it exactly matching with supported/configured data format in video pipeline?

Regards,

Brijesh

Hi, thank you for your reply!

Yes, I am using full range out. The format of my input data is YUV422 (yuyv).

I am familiar with the data stream of DSS on one side and find that there are many data conversions in video pipeline and video port.

For example, in the following transformation, the offset value of RGB is not 0, although it has been set to 0 in the driver file.

Is there a way to skip these transitions?

Looking forward to your reply!

Hi wang,

No, it is not recommended to skip these transformations. Internally DSS will first convert input YUV422 to RGB and do blending/color keying/transparency operations and then for BT output, it will be converted back into YUV422 format.

ok, could you please also check if the CSC matrix are matching? if YUV2RGB CSC is for BT601, then RGB2YUV matrix should be for BT601.

Also are you doing any brightness control? The output value should not change so much, unless these offsets are different.

Regards,

Brijesh

Hi, thank you for your reply!

No, I am not doing any brightness control. I dump the value of the register as follows. It is not the same as what is configured in the driver.

·Configuration in driver file

The value of dump:

| register | value |

| 0x04AA0008 | 0x00810042 |

| 0x04AA000C | 0x07DA0019 |

| 0x04AA0010 | 0x007007B6 |

| 0x04AA005C | 0x07A20070 |

| 0x04AA0060 | 0x000007EE |

| 0x04AA0068 | 0x00000000 |

| 0x04AA006C | 0x40004000 |

·Configuration in driver file

The value of dump:

| register | value |

| 0x04A60040 | 0x015F0100 |

| 0x04A60044 | 0x01000000 |

| 0x04A60048 | 0x07AA074D |

| 0x04A6004C | 0x00000100 |

| 0x04A60050 | 0x000001BB |

| 0x04A60054 | 0xC0000000 |

| 0x04A60058 | 0x0000C000 |

| 0x04A60023 | 0x00280AFD |

From the values of the above registers, it is found that, the offset value of RGB is not 0, although it has been set to 0 in the driver file.

How to locate the problem?

Looking forward to your reply!

Hi wang,

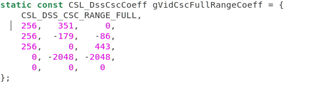

DSS outputs 20bit data for the BT1120 output format, but you could ignore lower 2 bits in each component and connect 16bits to your encoder. So although i see data0 data output line in the second image, it seems you are connect upper 8bits, so it looks correct.

Regards,

Brijesh

Hi,

Can you please confirm that the value at the offset 0x04A6023C is 0x00280AFD? If this is the case, the post offset are wrong..

Other offsets/coefficients for YUV2RGB conversion looks fine.

Regards,

Brijesh

Hi, thank you for your reply!

OK, I will check the value of the register (0x04A6023C).

Can't dpi0 be configured in bt.1120-16bit mode?If I can, how can I confirm that I am configuring 16 bit mode? I always thought it was determined by the following(ti-processor-sdk-rtos-j721e-evm-07_02_00_06/vision_apps/utils/dss/src/app_dss_defaults.c) parameters, but later I found that it works on the following configuration.Does this configuration determine the mode of BT(bt1120.16bit or bt1120.20bit)?

Driver file configuration:

DSS0_VP_CONTROL Register:

Looking forward to your reply!

Hi,

Please dont change output interface width to 16bit. This will reduce RGB888 output from overlay manager to RGB565. Please keep it 24bit output.

This overlay output will go to CSC for YUV conversion and then BT module to convert it into BT656/1120 output format. And finally it will be output on DPI0 output lines..

By default, m, k and hue parameters are not configured..

Regards,

Brijesh

Hi, thank you for your reply!

In hardware connection, I should keep Data0, 1, 2, 3, 4, 5, 6, 7, 10, 11, 12, 13, 14, 15, 16, 17 instead of data2, 3, 4, 5, 6, 7, 8, 9, 12, 13, 14, 15, 16, 17, 18, 19?

Looking forward to your reply!

Hi wang,

No, if you want to use 16bit, then connect D2 to D9 and D12 to D19 data lines..

Regards,

Brijesh

What i wanted to say in my previous post is, please dont change value of videoIfWidth variable, please keep it to APP_DCTRL_VIFW_24BIT.

Rgds,

Brijesh

Hi, thank you for your reply!

So far, I have checked the following links:

1、

·VC1 range mapping disabled

·Luma key operation is disabled

·Gamma inversion is disabled

·The matrix configuration of CSC is the same as that in the driver file

·Full range

The value of DSS0_VID_ATTRIBUTES register (0x04A60020) is : 0x00280AFD

The value of DSS0_VID_ATTRIBUTES2 register (0x04A60024) is: 0x3C000000

2、

·Full range

·The matrix configuration of CSC is the same as that in the driver file

·Gamma disabled

·APP_DCTRL_VIFW_24BIT

The value of DSS0_VP_CONFIG register (0x04AA0000) is: 0x03200000

The value of DSS0_COMMON_DISPC_CONNECTIONS register (0x04A000E4) is: 0x00000002

The value of DSS0_VP_CONTROL register (0x04AA0004) is: 0x00000361

3、Hardware circuit connection:

use 16bit, connect D2 to D9 and D12 to D19 data lines

4、YUV test procedure is as follows

#include "shm.h"

#include <TI/j7.h>

#include <TI/tivx.h>

#include <VX/vx.h>

#include <string.h>

#include <sys/types.h>

#include <sys/ipc.h>

#include <sys/shm.h>

#include <stdio.h>

#include <signal.h>

#include <dirent.h>

#include <errno.h>

#include <time.h>

#define DISPLAY_NUM_RUN_COUNT 100

//#define FILE_DIR "/opt/vision_apps/test_data/dttest"

typedef struct {

const char *name;

uint32_t pipeId;

uint32_t dataFormat;

uint32_t inWidth;

uint32_t inHeight;

uint32_t bpp;

uint32_t pitchY;

uint32_t pitchUV;

uint32_t outWidth;

uint32_t outHeight;

uint32_t posX;

uint32_t posY;

uint32_t loopCount;

} Arg;

/**

* @brief Add time stamp to bt1120 image

* @param addr: Bt1120 binary image sequence

* @param timestamp: 64 bit timestamp, small end representation

*/

static int fill_time_stamp(void *addr, unsigned long long *timestamp) {

char *addrp = (char *)addr;

int i = 0;

for (i = 15; i >= 0; i--)

addrp[15 - i] =

0x50 |

((uint8_t)(((*timestamp) & ((uint64_t)0xf << (i * 4))) >> (i * 4)));

return 0;

}

#if 1

static vx_status readYUV422Input(char *file_name, unsigned char *data_ptr) {

vx_status status = VX_SUCCESS;

if (status == VX_SUCCESS) {

FILE *fp = fopen(file_name, "rb");

if (fp == NULL) {

printf("Unable to open file %s \n", file_name);

return (VX_FAILURE);

}

vx_uint32 img_width = 1920;

vx_uint32 img_height = 1080;

// Copy YuYv

vx_uint32 num_bytes = fread(data_ptr, 1, img_width * img_height * 2, fp);

if (num_bytes != (img_width * img_height * 2))

printf("CbCr bytes read = %d, expected = %d \n", num_bytes,

img_width * img_height * 2);

fclose(fp);

}

return (status);

}

#endif

vx_status app_tidl_od_main(vx_int32 argc, vx_char *argv[]) {

vx_status status = VX_SUCCESS;

unsigned char gTiovxCtDisplayArray1[1920 * 1080 * 2] = {0};

Arg arg_;

arg_.pipeId = 2;

arg_.dataFormat = VX_DF_IMAGE_YUYV;

arg_.inWidth = 1920;

arg_.inHeight = 1080;

arg_.bpp = 2;

arg_.pitchY = 1920;

arg_.pitchUV = 0;

arg_.outWidth = 1920;

arg_.outHeight = 1080;

arg_.posX = 0;

arg_.posY = 0;

vx_context context = vxCreateContext();

status = vxGetStatus((vx_reference)context);

if (status != VX_SUCCESS) {

printf("vxGetStatus is failed! \n");

}

vx_image disp_image = 0;

vx_imagepatch_addressing_t image_addr;

tivx_display_params_t params;

vx_user_data_object param_obj;

vx_graph graph = 0;

vx_node node = 0;

//uint32_t loop_count = arg_.loopCount;

if (vx_true_e == tivxIsTargetEnabled(TIVX_TARGET_DISPLAY1))

{

tivxHwaLoadKernels(context);

disp_image = vxCreateImage(context, arg_.inWidth, arg_.inHeight, arg_.dataFormat);

image_addr.dim_x = arg_.inWidth;

image_addr.dim_y = arg_.inHeight;

image_addr.stride_x = arg_.bpp;

image_addr.stride_y = arg_.pitchY * 2;

image_addr.scale_x = VX_SCALE_UNITY;

image_addr.scale_y = VX_SCALE_UNITY;

image_addr.step_x = 1;

image_addr.step_y = 1;

vx_rectangle_t rect;

rect.start_x = 0;

rect.start_y = 0;

rect.end_x = arg_.inWidth;

rect.end_y = arg_.inHeight;

DIR * dir;

char *FILE_DIR = "/opt/vision_apps/test_data/dttest";

struct dirent * ptr;

dir = opendir(FILE_DIR);

if(NULL == dir)

{

printf("opendir error...!\n");

printf("%s\n",strerror(errno));

return -1;

}

char file_name[512] = {0};

loop1:

ptr = readdir(dir);

sprintf(file_name,"%s/%s",FILE_DIR,ptr->d_name);

if(!(strcmp(ptr->d_name,".")) || !(strcmp(ptr->d_name,"..")))

{

goto loop1;

}

printf("filename is-->%s\n",file_name);

if(ptr != NULL)

{

status = readYUV422Input(file_name,gTiovxCtDisplayArray1);

if (status != VX_SUCCESS)

{

printf("readYUV422Input is failed! \n");

}

}

long long current_time = time(0);

fill_time_stamp((void *)gTiovxCtDisplayArray1,(unsigned long long*)¤t_time);

status = vxCopyImagePatch(disp_image, &rect, 0, &image_addr,

(void *)gTiovxCtDisplayArray1, VX_WRITE_ONLY,

VX_MEMORY_TYPE_HOST);

if (status != VX_SUCCESS) {

printf("vxCopyImagePatch 0 is failed! \n");

}

memset(¶ms, 0, sizeof(tivx_display_params_t));

params.opMode = TIVX_KERNEL_DISPLAY_BUFFER_COPY_MODE;

params.pipeId = arg_.pipeId;

params.outWidth = arg_.outWidth;

params.outHeight = arg_.outHeight;

params.posX = arg_.posX;

params.posY = arg_.posY;

param_obj = vxCreateUserDataObject(context, "tivx_display_params_t",

sizeof(tivx_display_params_t), ¶ms);

graph = vxCreateGraph(context);

node = tivxDisplayNode(graph, param_obj, disp_image);

status = vxSetNodeTarget(node, VX_TARGET_STRING, TIVX_TARGET_DISPLAY1);

if (status != VX_SUCCESS) {

printf("vxSetNodeTarget is failed! \n");

}

status = vxVerifyGraph(graph);

if (status != VX_SUCCESS) {

printf("vxVerifyGraph is failed! \n");

}

while(1)

{

while ((ptr=readdir(dir))!= NULL)

{

if(!(strcmp(ptr->d_name,".")) || !(strcmp(ptr->d_name,"..")))

{

continue;

}

sprintf(file_name,"%s/%s",FILE_DIR,ptr->d_name);

printf("filename is-->%s\n",file_name);

status = readYUV422Input(file_name,gTiovxCtDisplayArray1);

if(status != VX_SUCCESS)

{

printf("readYUV422Input is failed! \n");

}

current_time = time(0);

fill_time_stamp((void *)gTiovxCtDisplayArray1,(unsigned long long*)¤t_time);

status = vxProcessGraph(graph);

if (status != VX_SUCCESS) {

printf("vxProcessGraph is failed!\n");

} else {

printf("vxProcessGraph is successed!\n");

}

status = vxCopyImagePatch(disp_image, &rect, 0, &image_addr,

(void *)gTiovxCtDisplayArray1, VX_WRITE_ONLY,

VX_MEMORY_TYPE_HOST);

if (status == VX_SUCCESS) {

printf("vxCopyImagePatch 1 is success! \n");

} else {

printf("in while(1),vxCopyImagePatch error\n");

//goto exit;

}

}

dir = opendir(FILE_DIR);

if(NULL == dir)

{

printf("opendir2 error...!\n");

printf("%s\n",strerror(errno));

printf("break while(1)...!!!\n");

break;

}

}

vxReleaseNode(&node);

vxReleaseGraph(&graph);

vxReleaseImage(&disp_image);

vxReleaseUserDataObject(¶m_obj);

tivxHwaUnLoadKernels(context);

}

return status;

}

#if 0

TEST_WITH_ARG(tivxHwaDisplay, testZeroBufferCopyMode, Arg, PARAMETERS)

{

vx_context context = context_->vx_context_;

vx_image disp_image[2];

vx_imagepatch_addressing_t image_addr;

tivx_display_params_t params;

vx_user_data_object param_obj;

vx_graph graph = 0;

vx_node node = 0;

vx_image disp_image_temp;

uint32_t num_refs;

uint32_t loop_count = arg_.loopCount;

vx_graph_parameter_queue_params_t graph_parameters_queue_params_list[1];

if (vx_true_e == tivxIsTargetEnabled(TIVX_TARGET_DISPLAY1))

{

tivxHwaLoadKernels(context);

CT_RegisterForGarbageCollection(context, ct_teardown_hwa_kernels, CT_GC_OBJECT);

ASSERT_VX_OBJECT(disp_image[0] = vxCreateImage(context, arg_.inWidth, arg_.inHeight, arg_.dataFormat), VX_TYPE_IMAGE);

ASSERT_VX_OBJECT(disp_image[1] = vxCreateImage(context, arg_.inWidth, arg_.inHeight, arg_.dataFormat), VX_TYPE_IMAGE);

image_addr.dim_x = arg_.inWidth;

image_addr.dim_y = arg_.inHeight;

image_addr.stride_x = arg_.bpp;

image_addr.stride_y = arg_.pitchY;

image_addr.scale_x = VX_SCALE_UNITY;

image_addr.scale_y = VX_SCALE_UNITY;

image_addr.step_x = 1;

image_addr.step_y = 1;

vx_rectangle_t rect;

rect.start_x = 0;

rect.start_y = 0;

rect.end_x = arg_.inWidth;

rect.end_y = arg_.inHeight;

vxCopyImagePatch(disp_image[0],

&rect,

0,

&image_addr,

(void *)gTiovxCtDisplayArray1,

VX_WRITE_ONLY,

VX_MEMORY_TYPE_HOST

);

vxCopyImagePatch(disp_image[1],

&rect,

0,

&image_addr,

(void *)gTiovxCtDisplayArray2,

VX_WRITE_ONLY,

VX_MEMORY_TYPE_HOST

);

memset(¶ms, 0, sizeof(tivx_display_params_t));

params.opMode=TIVX_KERNEL_DISPLAY_ZERO_BUFFER_COPY_MODE;

params.pipeId=arg_.pipeId;

params.outWidth=arg_.outWidth;

params.outHeight=arg_.outHeight;

params.posX=arg_.posX;

params.posY=arg_.posY;

ASSERT_VX_OBJECT(param_obj = vxCreateUserDataObject(context, "tivx_display_params_t", sizeof(tivx_display_params_t), ¶ms), (enum vx_type_e)VX_TYPE_USER_DATA_OBJECT);

ASSERT_VX_OBJECT(graph = vxCreateGraph(context), VX_TYPE_GRAPH);

ASSERT_VX_OBJECT(node = tivxDisplayNode(graph, param_obj, disp_image[0]), VX_TYPE_NODE);

VX_CALL(vxSetNodeTarget(node, VX_TARGET_STRING, TIVX_TARGET_DISPLAY1));

/* Image is parameter number 1 for Display Node and becomes graph parameter 0 */

add_graph_parameter_by_node_index(graph, node, 1);

/* Set graph schedule config such that graph parameter @ index 0 is enqueuable */

graph_parameters_queue_params_list[0].graph_parameter_index = 0;

graph_parameters_queue_params_list[0].refs_list_size = 2; /* Two images */

graph_parameters_queue_params_list[0].refs_list = (vx_reference*)&disp_image[0];

/* Schedule mode auto is used, here we don't need to call vxScheduleGraph

* Graph gets scheduled automatically as refs are enqueued to it

*/

vxSetGraphScheduleConfig(graph,

VX_GRAPH_SCHEDULE_MODE_QUEUE_AUTO,

1,

graph_parameters_queue_params_list

);

/* Explicitly set graph pipeline depth */

ASSERT_EQ_VX_STATUS(VX_SUCCESS, set_graph_pipeline_depth(graph, 2));

VX_CALL(vxVerifyGraph(graph));

/* Enqueue input references */

vxGraphParameterEnqueueReadyRef(graph, 0, (vx_reference*)&disp_image[0], 1);

vxGraphParameterEnqueueReadyRef(graph, 0, (vx_reference*)&disp_image[1], 1);

/* Wait for the loop count */

while(loop_count-- > 0)

{

/* Dequeue one image buffer */

vxGraphParameterDequeueDoneRef(graph, 0, (vx_reference*)&disp_image_temp, 1, &num_refs);

/* Enqueue the same image buffer */

vxGraphParameterEnqueueReadyRef(graph, 0, (vx_reference*)&disp_image_temp, 1);

}

/* ensure all graph processing is complete */

vxWaitGraph(graph);

VX_CALL(vxReleaseNode(&node));

VX_CALL(vxReleaseGraph(&graph));

VX_CALL(vxReleaseImage(&disp_image[0]));

VX_CALL(vxReleaseImage(&disp_image[1]));

VX_CALL(vxReleaseUserDataObject(¶m_obj));

ASSERT(node == 0);

ASSERT(graph == 0);

ASSERT(disp_image[0] == 0);

ASSERT(disp_image[1] == 0);

ASSERT(param_obj == 0);

tivxHwaUnLoadKernels(context);

}

}

TESTCASE_TESTS(tivxHwaDisplay,

testBufferCopyMode,

testZeroBufferCopyMode

)

#endif

hi wang,

The register settings look fine. BT1120 and CSC are enabled, DPI is enabled, DPI0 is connected to VP2. it looks to be correct.

Instead of connecting any video pipeline, can you please just display background color. you could set the background color to 0 and analyze luma output, it should almost 0x0, so all data lines should be low, except when it is transmitting sync codes.. Can you check this?

Regards,

Brijesh

Hi, thank you for your reply!

This is my overlay configuration:

The oscilloscope detects that there is a signal in Data0、Data4、Data15.

Received pictures (after YUV422 to nv12), as follows:

Y component:

UV component:

What is the reason?

Looking forward to your reply!

Hi,

all data lines will toggle, because of the SAV and EAV codes. But the received image looks almost black ie when luma has almost 0 value and chrome is 0x80, it is black color.

So output looks correct.

Regards,

Brijesh

Hi,

How are you checking the output? Are you viewing it some yuv viewer?

Can you change background color to, lets say red, or blue and check the output in some viewer?

Regards,

Brijesh

Hi, thank you for your reply!

First of all, the input of DSS is a yuv422i-yuyv image with full 0 (Y component and UV component are both 0).

Then there are three ways to detect the output.

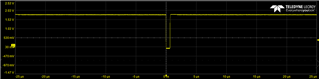

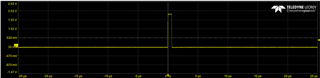

1、The first one is to use the oscilloscope to check the waveform of 30us (there are about 1080 pixels when the clock is 74.25mhz), and find a lot of non-zero data, as follows:

Why do 0 and 1 have different trigger waveforms?

2、With YUV image viewer, it is found that the original image is different from the received image.

After all 0 pictures are transmitted, the colors are different,as follows:

As shown below, the color in the red box is different:

3、Open the file in hexadecimal and find that the Y and UV components have changed after transmission