Hi,

I have a question from my customer about QSPI read cycle.

He is trying to read data from QSPI flash, but read data are 1byte shifted as below.

Written data: 0x00000000, 0x12345678

Read data: 0x00000012, 0x34567800

He checked QSPI waveform and wonders dummy cycles are not aligned between Flash and K2G.

As you can see below waveform, the flash memory send data 8 cycles after address field.

But it seems K2G side takes the 1st read byte 6 cycles after address field.

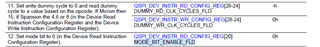

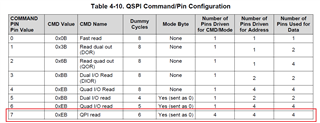

Register configurations are below.

DUMMY_RD_CYCLES_FLD=0x4 and MODE_BIT_ENABLE_FLD=0x1, so total cycles are 4+2=6 cycles.

Then customer changed DUMMY_RD_CYCLES_FLD, but waveform did not change.

Is there any missing configuration to change dummy cycles?

Thanks and regards,

Koichiro Tashiro

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.