I want to use HRPWM capability of the ePWM module. I use to transfer the CMPA AND CMPAHR data through EDMA triggered by the SOCA signal. It works very fine.

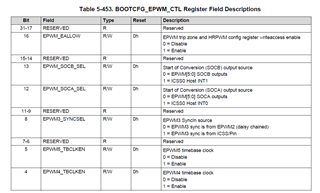

My main problem I can not write into the HRCTL Register to set DELMODE to 2h. Table 11-829 does not say it is protected. Nevertheless I tried to set EPWM_EALLOW bit of EPWM_CTL Register but no success. Can you verify that?

My configuration is attached:

/* Function to setup PWM module one-time configurations */

void PWM_init(){

/*Time base clock configuring using prescaler*/

CSL_epwmTbTimebaseClkCfg(CSL_PWM_3_CFG_REGS, TBCLK_FREQ, MODULE_CLK);

CSL_epwmTbTimebaseClkCfg(CSL_PWM_4_CFG_REGS, TBCLK_FREQ, MODULE_CLK);

/*Sync 3A and PWM5A*/

// CSL_epwmTbSyncEnable(CSL_PWM_3_CFG_REGS, 0, CSL_EPWM_TB_CNT_DIR_AFT_SYNC_UP);

CSL_epwmTbSetSyncOutMode(CSL_PWM_3_CFG_REGS,CSL_EPWM_TB_SYNC_OUT_EVT_CNT_EQ_ZERO);

CSL_epwmTbSyncEnable(CSL_PWM_4_CFG_REGS, 0, CSL_EPWM_TB_CNT_DIR_AFT_SYNC_UP);

/*Configuring the EPWM_AQCTLA register*/

CSL_epwmAqActionOnOutputCfg(CSL_PWM_3_CFG_REGS, CSL_EPWM_OUTPUT_CH_A, &aqctrla);

CSL_epwmAqActionOnOutputCfg(CSL_PWM_3_CFG_REGS, CSL_EPWM_OUTPUT_CH_B, &aqctrlb);

CSL_epwmAqActionOnOutputCfg(CSL_PWM_4_CFG_REGS, CSL_EPWM_OUTPUT_CH_A, &aqctrla);

/*Set frequency*/

CSL_epwmTbPwmFreqCfg(CSL_PWM_3_CFG_REGS, TBCLK_FREQ, PWM_FREQ2, TB_COUNT_UP, TB_IMMEDIATE);

CSL_epwmTbPwmFreqCfg(CSL_PWM_4_CFG_REGS, TBCLK_FREQ, PWM_FREQ, TB_COUNT_UP, TB_IMMEDIATE);

CSL_epwmCounterComparatorCfg(CSL_PWM_3_CFG_REGS, CSL_EPWM_CC_CMP_A, (int)1041, CC_SHADOW, CC_CTR_ZERO, OVER_WRITE_SHADOW_DISABLED);

CSL_epwmCounterComparatorCfg(CSL_PWM_4_CFG_REGS, CSL_EPWM_CC_CMP_A, (int)260, CC_SHADOW, CC_CTR_ZERO, OVER_WRITE_SHADOW_DISABLED);

// CSL_epwmHrLoadCmpAHrValue(CSL_PWM_3_CFG_REGS,1,CSL_EPWM_HR_REG_ACT_LOAD_CNT_ZRO_PULSE);

/*Set SOCA for EDMA PWM */

HW_WR_REG16(0x021D0C32,0x900);

HW_WR_REG16(0x021D0C34,0x500);

//Set EALLOW

HW_WR_REG32(0x021D0C00, 0x438);

//SETUP EPWM DELMODE to falling edge

HW_WR_REG16(0x021D0CC0,0x0);

HW_WR_REG16(0x021D0CC0,0x2);

//Clear EALLOW

HW_WR_REG32((CSL_BOOT_CFG_REGS + BOOTCFG_EPWM_CTL_REG_OFFSET), 0x38);

// CSL_epwmHighResolutionCfg(CSL_PWM_3_CFG_REGS,CSL_EPWM_HR_DELAY_BUS_SEL_CMPAHR, CSL_EPWM_HR_DELAY_EDGE_CTRL_FALLING);

}

Further more in the TRM is a link error. 11.5.3 is linked to 11.6.3.