Hi all,

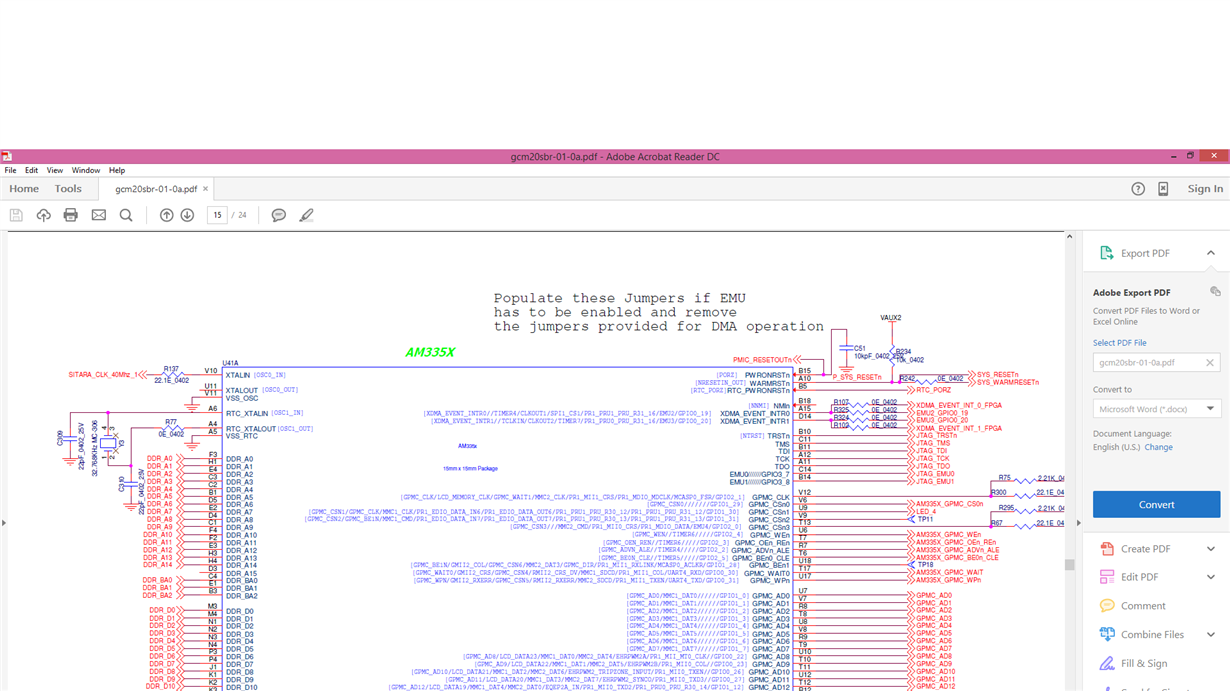

we have developed custom board with am3359 processor. we are not getting CCCC ASCII char printed on console.

Setting SYSBOOT[5] = 1 will output the system clock on CLKOUT1 we are able to monitor the clock

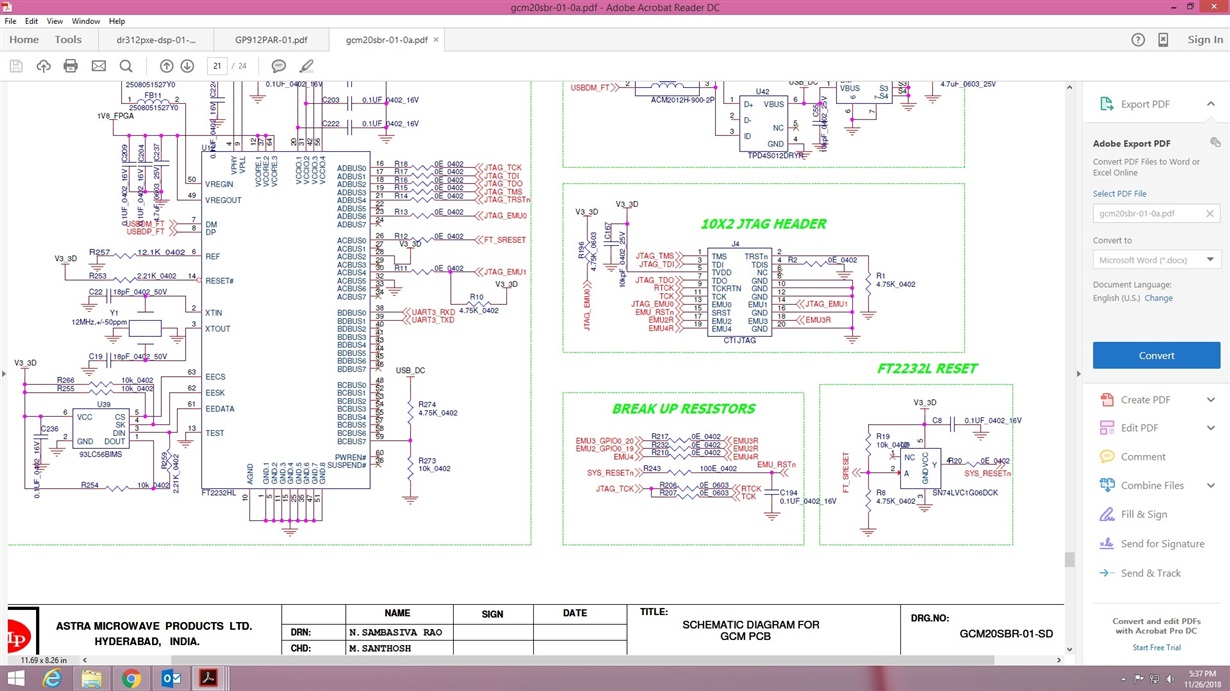

using Analyzing Boot Issues with CCS and JTAG we are able to test the connection, but when trying to run the script following error is displayed

js:> loadJSFile /home/astra/Downloads/am335x-boot.dss

Error connecting to the target: emulation failure occurred (/home/astra/Downloads/am335x-boot.dss#369)

CortxA8: Error connecting to the target: (Error -2062 @ 0x1851960) Unable to halt device. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 8.0.27.9)

Thanks in advance.