Our company is developing a product based in AM4372. We are having a problem with bringing up u-boot due to a RAM (DDR3) issue. To be more precise, if I run

get_ram_size( (void *)CONFIG_SYS_SDRAM_BASE, CONFIG_MAX_RAM_BANK_SIZE);

the result will always be “0” except if I use

const struct dpll_params gp_evm_dpll_ddr = { 50, 2, 1, -1, 2, -1, -1};

which will return “4”.

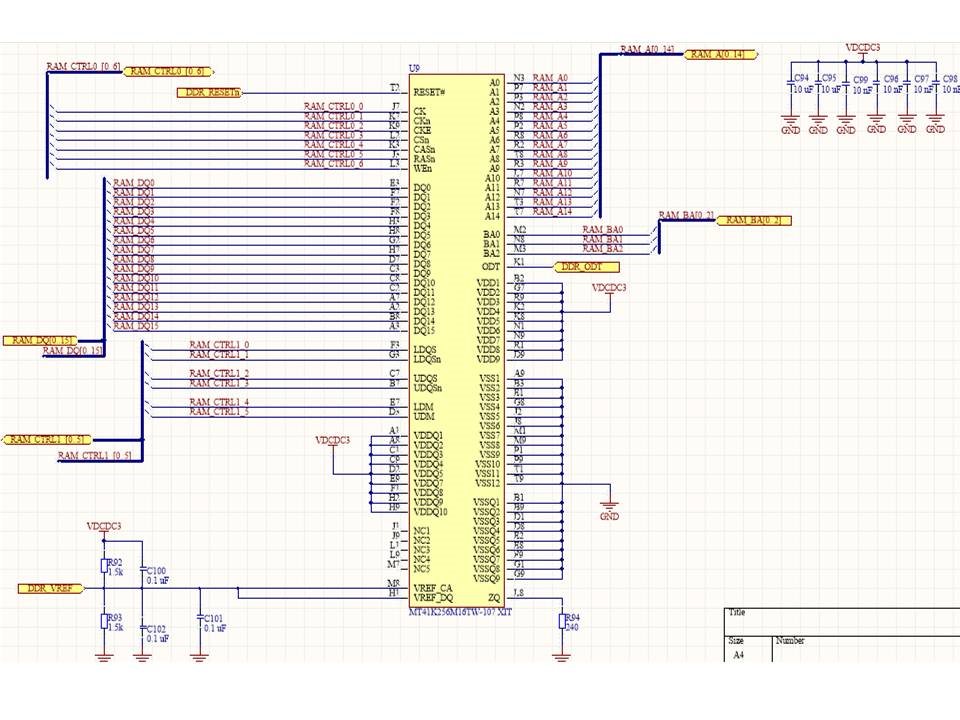

We are using a 24MHz crystal, and a MT41K256M16TW-107 XIT RAM memory.

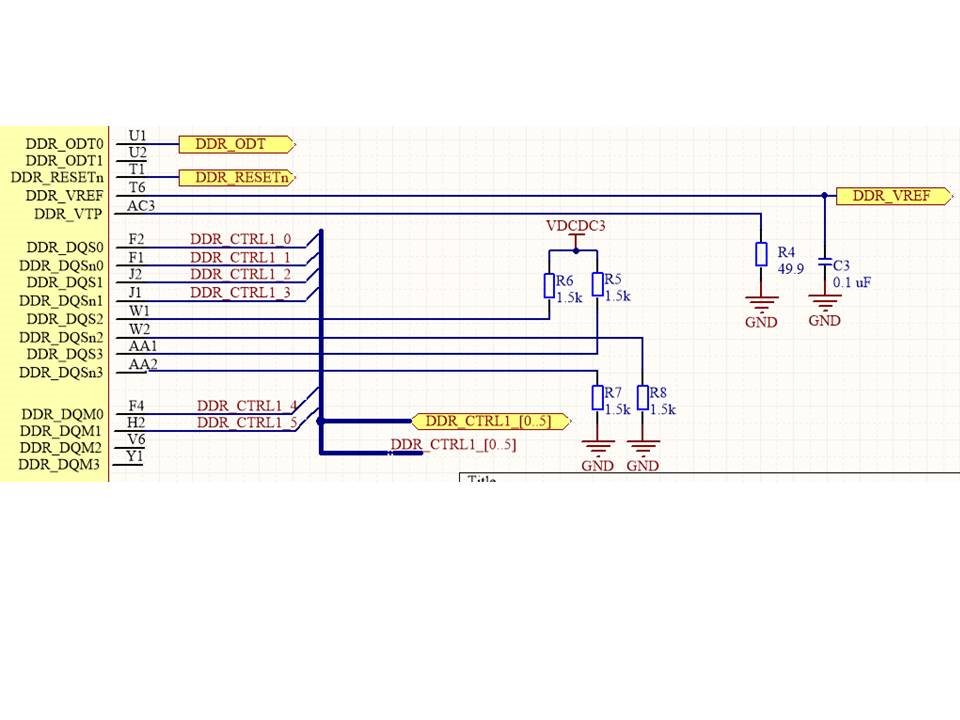

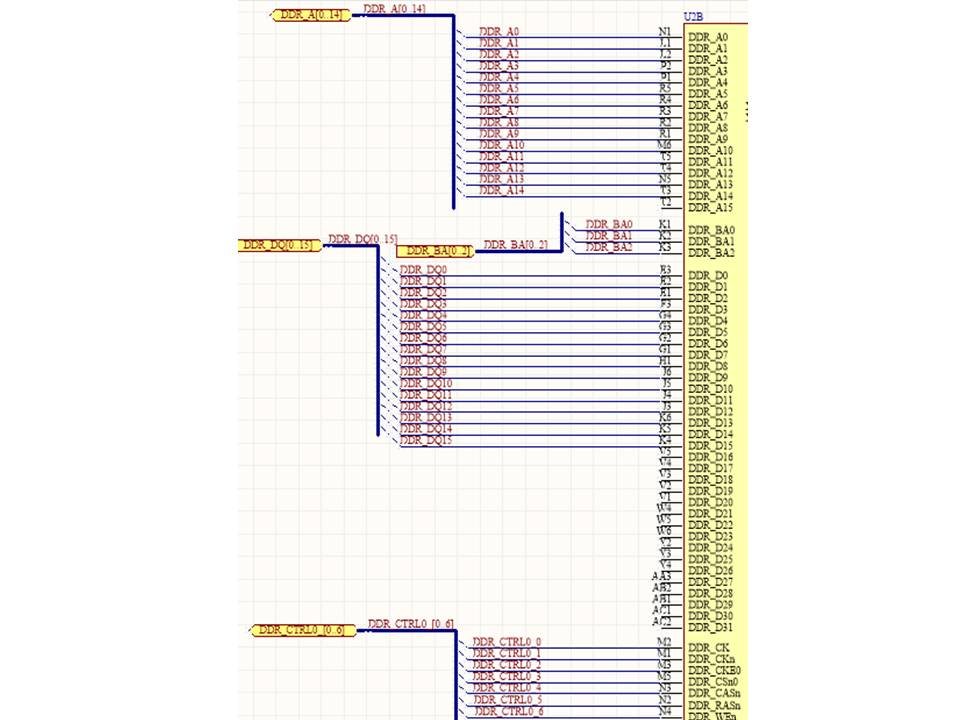

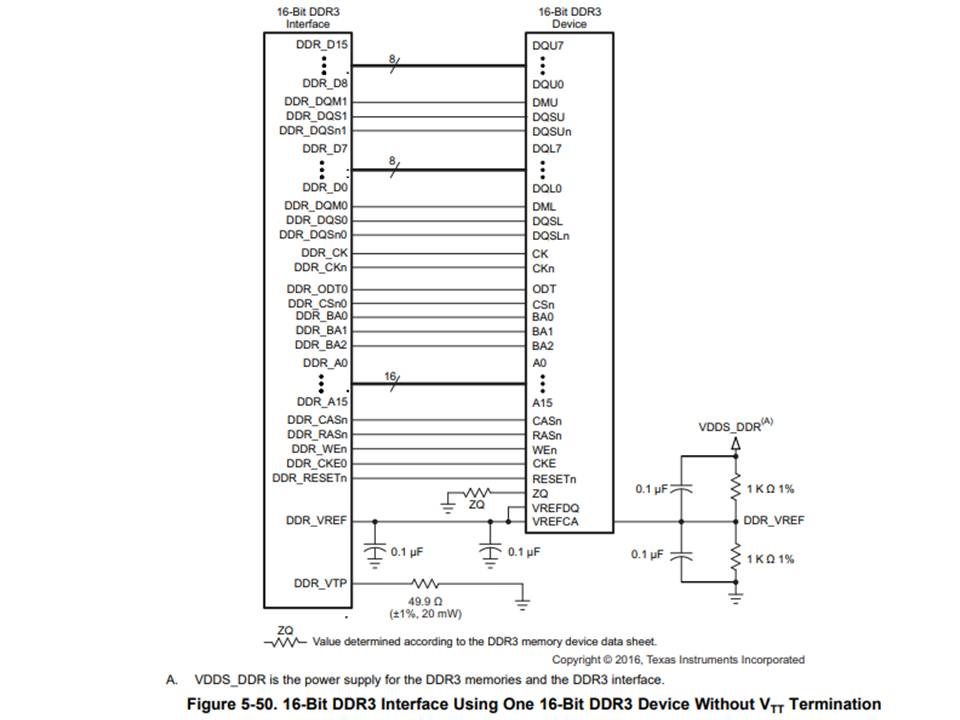

The connection for RAM memory it is according to AM437x Sitara Processors Datasheet, page 172, figure 5.50. 16-Bit DDR3 interface using one 16-Bit DDR3 module without VTT termination (see ConnectionRAM.jpg). This image refers to our schematic design. Please note that R5, R6, R7, R8, R92 and R93 are 1.5k (AM4372-RAM1.jpg, AM4372-RAM2.jpg, SematicRAM.jpg).

Following the instructions in “AM43xx EMIF Tools” documentation, we have compiled the Excel file according the information retrieved from the RAM module datasheet (datasheet.pdf)

This is what have set:

const struct dpll_params gp_evm_dpll_ddr = {

50, 2, 1, -1, 4, -1, -1};

static const struct emif_regs ddr3_smaway_emif_regs_400Mhz = {

.sdram_config = 0x60A05332,

.sdram_config2 = 0x00000000,

.ref_ctrl = 0x00000c30,

.sdram_tim1 = 0xEAAAE51B,

.sdram_tim2 = 0x266B7FDA,

.sdram_tim3 = 0x5F7F867F,

.read_idle_ctrl = 0x00050000,

.zq_config = 0x50077D33,

.temp_alert_config = 0x00000000,

.emif_ddr_phy_ctlr_1 = 0x00048009,

.emif_ddr_ext_phy_ctrl_1 = 0x00040100,

.emif_ddr_ext_phy_ctrl_2 = 0x00000000,

.emif_ddr_ext_phy_ctrl_3 = 0x0000000e,

.emif_ddr_ext_phy_ctrl_4 = 0x00000000,

.emif_ddr_ext_phy_ctrl_5 = 0x00000000,

.emif_rd_wr_lvl_rmp_win = 0x00000000,

.emif_rd_wr_lvl_rmp_ctl = 0x00000000,

.emif_rd_wr_lvl_ctl = 0x00000000,

.emif_rd_wr_exec_thresh = 0x00000405,

.emif_prio_class_serv_map = 0x00000000,

.emif_connect_id_serv_1_map = 0x00000000,

.emif_connect_id_serv_2_map = 0x00000000,

.emif_cos_config = 0x00ffffff};

Any ideas what we could have done wrong?