Tool/software: TI C/C++ Compiler

Hello, ti experts,

My SDK version is PSDK-07_01_00_11.

Are there write protection restrictions on the operation of the CTRLMMR_PCIE_REFCLK1_CLKSEL register?

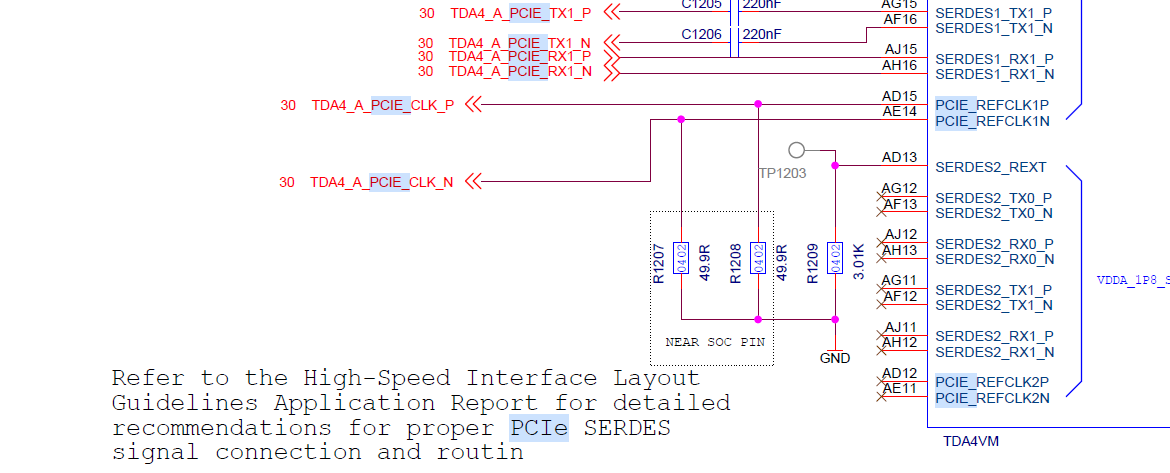

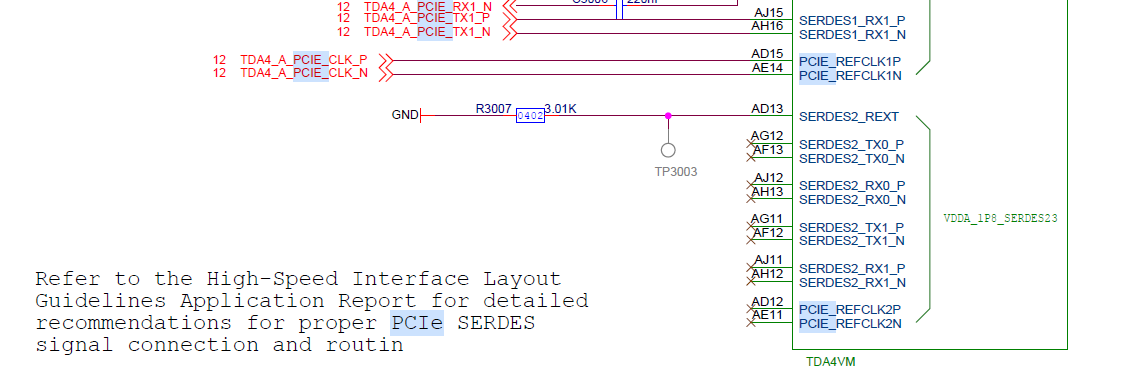

I am currently debugging PCIe's function of using internal clock output, using PCIe1.

Refer to the following post

I need to modify the following registers

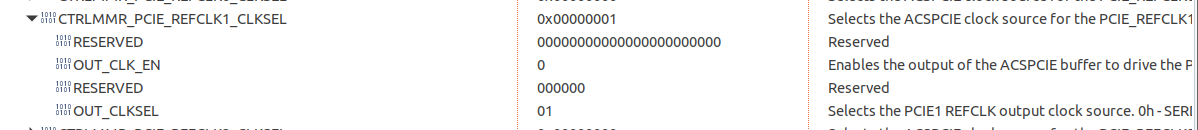

1. CTRLMMR_PCIE_REFCLK1_CLKSEL, bit8 is set to 1, and bit1~0 is set to 1;

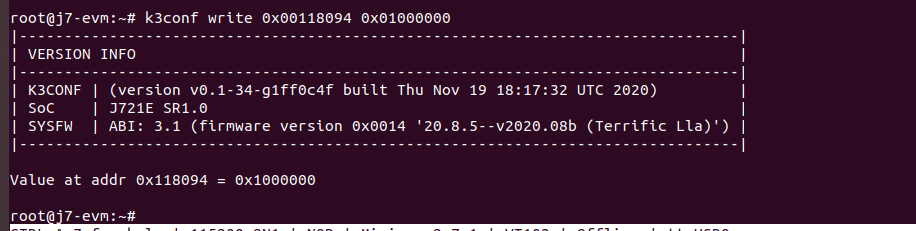

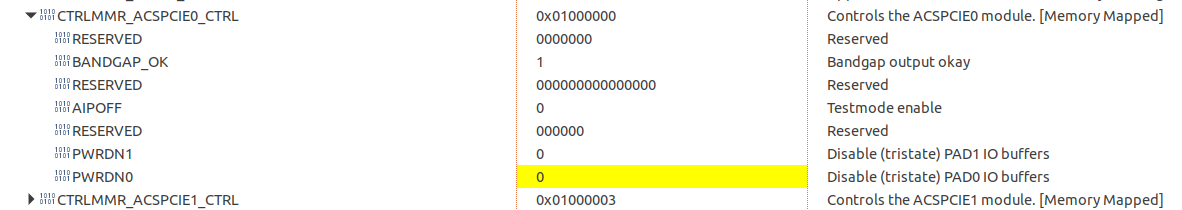

2.CTRLMMR_ACSPCIE1_CTRL; bit1 and bit0 are both set to 0

I tried three methods to modify the value of the register, CTRLMMR_PCIE_REFCLK1_CLKSEL can not be modified, always keep the default value 0x01; CTRLMMR_ACSPCIE1_CTRL can be modified;

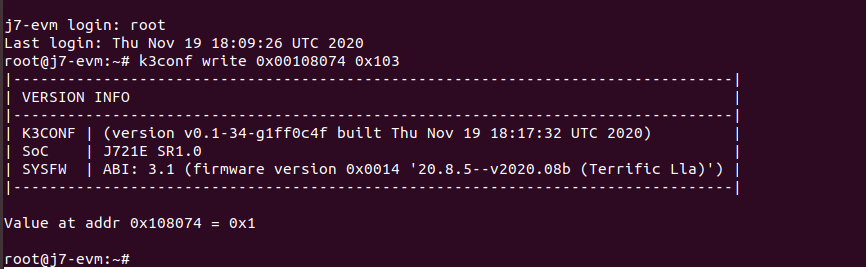

1. After starting the linux system, modify it through the k3conf write 0x00108074 0x103 instruction;

2. Use the ccs debug method to load vxlinux symbol on a72, and directly modify the register through ccs after startup.

3. Modify the linux device tree and driver code to achieve the modification;

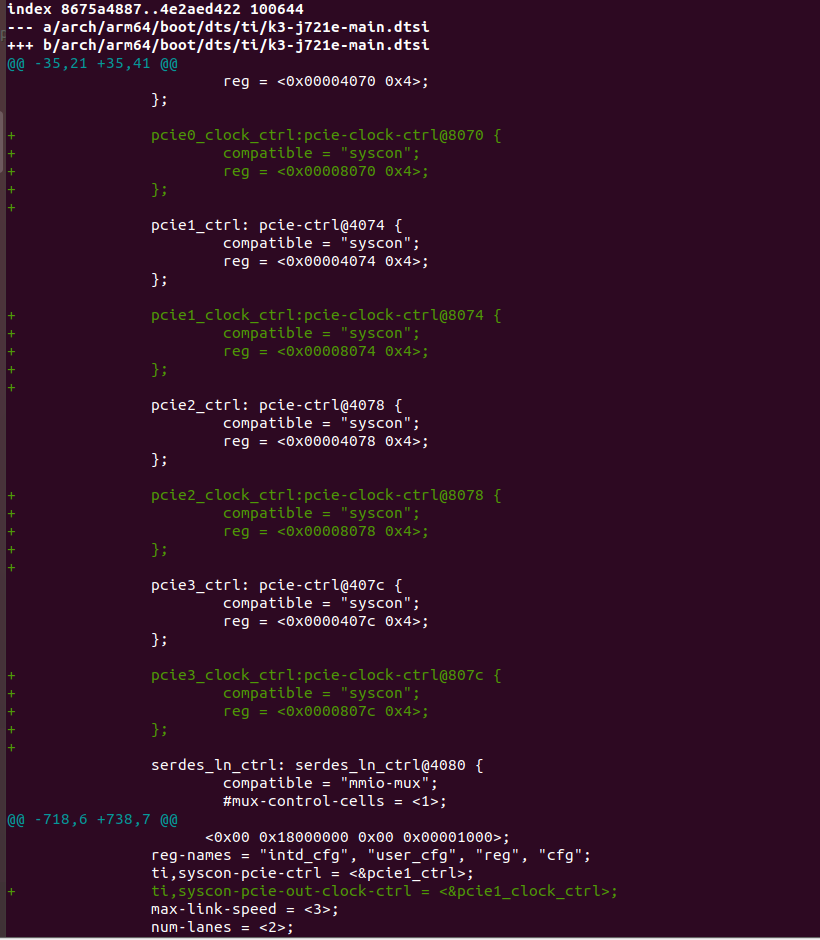

Add syscon option in dts file:

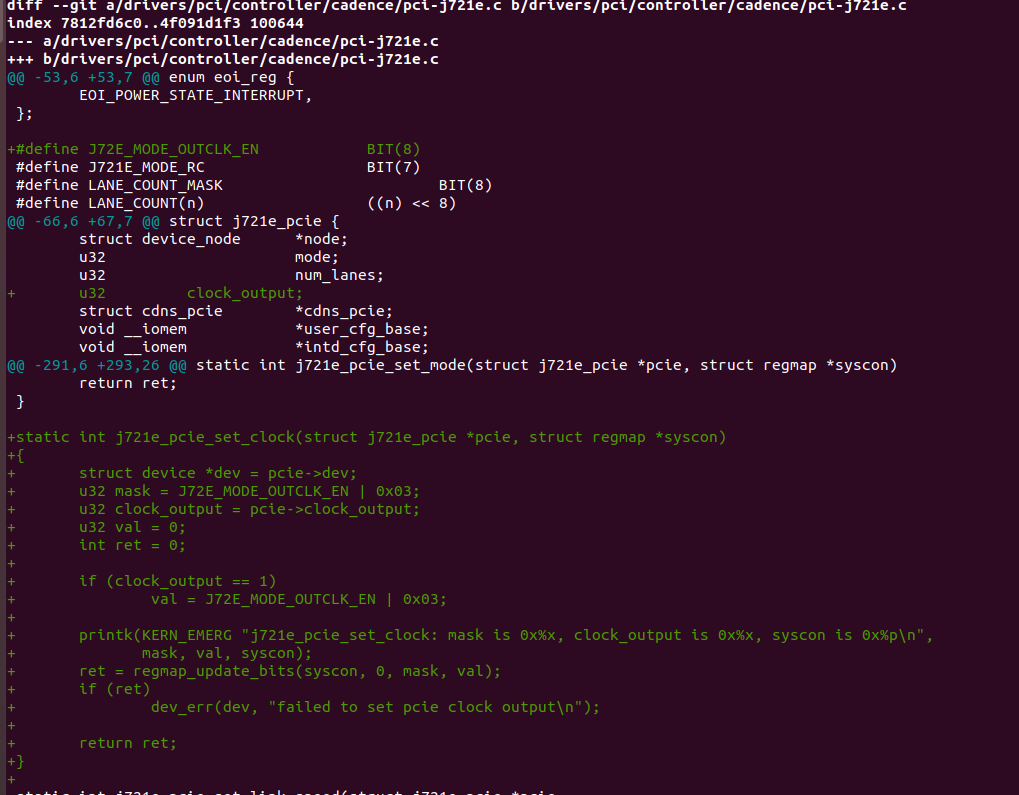

Make the following changes in the driver/pci/controller/cadence/pci_j72e.c file:

Then, start linux, use the same method as method 1 to read the register, the result is the same as method 1