- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hai team,

I am working on AFE7700 EVM initial bring up. I am testing the AFE7700 EVM without any FMC card. The Latte software version 5.6 is used for testing the board. The board is powered with 6V DC power supply and setup.py script is run to establish the connection between PC running Latte and the AFE7700 EVM.

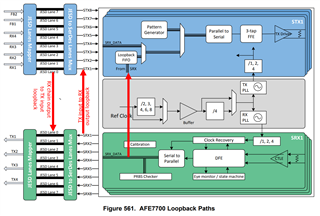

I want to check the internal loopback option which is mentioned in slose45a_AFE7700_datasheet_final section 9.3.10, Is there any register sequence to be followed and so please kindly help with the sequence.

Thanks in advance

Hi Soma,

When using AFE7700EVM without any FMC card, only useful loopback mode is the third one mentioned in datasheet i.e. receiver chain output data to transmitter chain input data at JESD204B/C logical lanes level. This loopback can be enabled by setting below parameter in bring-up script:

sysParams.jesdLoopbackEn = 1

Note that for this loopback mode, receiver and transmitter chains should be configured to the same JESD204B/C LMFS mode and equal lane rate.

You have to run setup.py, devInit.py and the modified bring-up script respectively to configure the AFE EVM.

Regards,

Vijay

Hai Vijay,

Thanks for your reply.

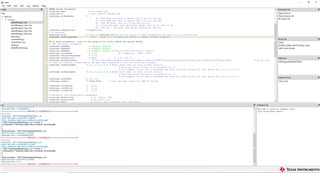

The above Settings are done in the besicBringup_1.py script.

sysParams.jesdLoopbackEn = 1

sysParams.LMFSHdRx = ["24410","24410"]

sysParams.LMFSHdTx = ["24410","24410"]

I am facing one error in the log window saying that

#Error: 'NoneType' object has no attribute 'rawWriteLogEn'

# "AFE77xx/bringup/basicBringup_1.py", line 89, in

# AttributeError: 'NoneType' object has no attribute 'rawWriteLogEn'

what is this error and how to resolve this error.

These changes are enough to validate this loopback are I need to configure any registers. I also want to know how to check this loopback setting are working.

Regards

Soma Sekhar

ERROR :

CODE :

setupParams.selectedDut=1

if boardType in ("EVM","HSC1373"):

if setupParams.selectedDut==1:

AFE=AFE1

device=device1

logDumpInst=logDumpInst1

else:

AFE=AFE0

device=device0

logDumpInst=logDumpInst0

else:

setupParams.selectedDut=0

sysParams=AFE.systemParams

device.hardReadAlways=False

##### System Parameters

sysParams.FRef = 491.52#368.64#

sysParams.Fs = 2949.12#56*61.44#3440.64#

sysParams.pllMuxModes = 0

#0: 4T4R Mode with PLL0 as Master. PLL 0 for all the LOs.

#1: 4T4R Mode with PLL2 as Master. PLL 2 for all the LOs.

#2: 4T4R FDD Mode. PLL0 for TX and PLL2 for RX.

#3: 2*2T2R FDD Mode: PLL0 AB-TX;PLL3 AB-RX; PLL2 CD TX; PLL4 CD RX

#4: 2T2R FDD - TDD Mode: PLL0 AB-TX; PLL3-AB-RX; PLL2 CD

sysParams.useSpiSysref = True#False#

# LO Settings

sysParams.pllLo = [3500.01,sysParams.Fs,3501.06,1800.24,3400.0] #PLL Frequencies for PLLs [0,1,2,3,4]#4899.9825

sysParams.jesdLoopbackEn = 1 #Make it 1 to Enable the JESDTX to JESDRX internal loopback

## In below parameters, first in the array is for first 2T2R1F and second 2T2R1F.

# JESD and Serdes Parameters

sysParams.LMFSHdRx = ["24410","24410"]

sysParams.LMFSHdFb = ["22420","22420"]

sysParams.LMFSHdTx = ["24410","24410"] #["44210","44210"]#["24410","24410"]

sysParams.systemMode = [1,1] # 0-Identical, 1-FDD, 2-TDD

sysParams.dedicatedLaneMode = [0,0]

sysParams.jesdProtocol = 0#1#0 # -0:B; 1:H; 2:C

sysParams.serdesFirmware =""#r"\\Mac\Home\Documents\Texas Instruments\Latte\lib\Afe77xxLibrary\resourceFiles\with_rom.fw.d04a4d.bin"False#True#"" # If you want to lead any firmware, please speify the path here. Otherwise it will not write any firmware

sysParams.jesdTxLaneMux = [0,1,2,3,4,5,6,7] # Enter which lanes you want in each location.

# Note that across 2T Mux is not possible in 0.5.

# For example, if you want to exchange the first two lines of each 2T, this should be [1,0,2,3,5,4,6,7]

sysParams.jesdRxLaneMux = [0,1,2,3,4,5,6,7] # Enter which lanes you want in each location.

# Note that across 2R Mux is not possible in 0.5.

# For example, if you want to exchange the first two lines of each 2R, this should be [1,0,2,3,5,4,6,7]

sysParams.jesdRxRbd = [15, 15]

sysParams.jesdScr = [True,True] # Does the Same config for JESD TX and RX

sysParams.lowIfNcoRx = [0,0]

sysParams.lowIfNcoTx = [0,0]

sysParams.lowIfNcoFb = [0,0]

# Decimation and interpolation Parameters

sysParams.ddcFactorRx = [8, 8]#[14, 14]#

sysParams.ddcFactorFb = [4, 4]#[7, 7]#

sysParams.fbNco = [3500.01,3500.01]#[4899.9825, 4899.9825]

sysParams.ducFactorTx = [4, 4]#[14, 14]#[28./3,28./3]#[7, 7]#

sysParams.setTxLoFbNcoFreqForTxCalib = True#False# # Note that if this is True, the fbNcoValues entered above will be overwritten and fbNCO and LO values will be chosen to the closest supported values.

sysParams.txIqMcCalibMode=0 # 0 -Single Fb Mode FB AB ; 1 -Single Fb Mode FB CD ; 2- Dual Fb_Mode

sysParams.customerConfig = False#True

LMKParams.pllEn = False#True# # If this is True, it takes the onboard oscillator as input to PLL and all clocks are generated from it. If it is False, it takes the external clock input of frequency - lmkParams.inputClk and generates the required clocks through dividers (No LMK PLL will be used).

LMKParams.lmkFrefClk = False#True

LMKParams.inputClk = 1474.56#1290.24#

LMKParams.sysrefFreq = 2949.12/1536.0

sysParams.bitFileType=0 #0-Regular. 1- Same clock rate to FPGA 2 inputs. 2-8-Lane codes

if simulationMode==False:

setupParams.skipFpga=0

setupParams.skipLmk=0

AFE.skipRxConfig=0

AFE.skipFbConfig=0

AFE.skipTxConfig=0

AFE.skipAgc=0

sysParams.enableRxDsaFactoryCal = False

sysParams.enableTxDsaFactoryCal = False

sysParams.enableTxIqmcLolTrackingCorr = False

sysParams.enableRxIqmcLolTrackingCorr = True

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\config.txt")

logDumpInst.logFormat=0x07

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.rewriteFile=1

device.rawWriteLogsFile=ASTERIX_DIR+DEVICES_DIR+r"\test.txt"#"D:\AFE77xx_config/testBroadcast.txt"

myfpga.rawWriteLogEn=0

lmk.rawWriteLogEn=0

myfpga.rawWriteLogsFile=device.rawWriteLogsFile

lmk.rawWriteLogsFile=device.rawWriteLogsFile

# AFE.initializeConfig()

AFE.deviceBringup()

device.rawWriteLogEn=1

myfpga.rawWriteLogEn=0

lmk.rawWriteLogEn=0

engine.sampleNo=32768

Hi Soma,

From the error you get, it looks like you didn't run devInit.py after running setup.py. You need to run setup.py and devInit.py (in that order) before running any bringup script.

You have to run setup.py, devInit.py and the modified bring-up script respectively

Also in the updated bringup script, Rx and TX data rates are not equal. That would cause lane rates of RX an TX to be not equal. You have to update sysParams.ducFactorTx to [8,8]. I will verify this script on an EVM and send you verified script tomorrow.

Regards,

Vijay

Hai Vijay,

Thanks for your response

I am following the same procedure what you have mentioned in the above comment.

Initially I run with the setup.py --> devlnit.py --> modified basicBringup_1.py script. image is also attached for reference.

As you mentioned in the above comment I have changed the sysParams.ducFactorTx to [8,8] in the basicBringup_1.py script even thought I am facing the same error in the log window. I also attached the error image for reference. Kindly help me to complete this task.

Regards,

Soma

Hi Soma,

Did you follow instructions from the document named "Latte_Upgrade_Instructions.docx" in secure folder?

Can you update 'basicBringup_Case-2.py' for JESD loopback mode and run. Let me know if you still see errors when running the script.

I ran into JESD link-up issues when testing the JESD loopback mode in TI lab. I check once again tomorrow and update you.

Regards,

Vijay

Hai Vijay,

I followed the steps given in Latte_Upgrade_Instructions.docx. As per the document I am using Latte Version : 5.2.3

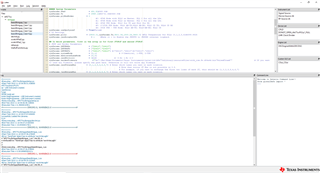

I ran the basicBringup_case2.py with the following changes

sysParams.jesdLoopbackEn = 1

since LMFS for TX and RX and data rate for TX and RX are given same, so I have changed it.

I didn't found any error while running the basicBringup_case2.py script. But there is status of link. I have pasted the log data here can you please check this once.

LOG WINDOW :

#======

#Executing .. AFE77xx/bringup/setup.py

#Start Time 2022-11-10 13:15:34.745000

AFE77xxLibraryPG1P1

spi - USB Instrument created.

resetDevice

Purge

MPSSE mode set

Kintex RegProgrammer - USB Instrument created.

Kintex RegProgrammer - USB Instrument created.

#Done executing .. AFE77xx/bringup/setup.py

#End Time 2022-11-10 13:15:41.254000

#Execution Time = 6.50900006294 s

#================ ERRORS:0, WARNINGS:0 ================#

#======

#Executing .. AFE77xx/bringup/devInit.py

#Start Time 2022-11-10 13:15:50.189000

Successfully Loaded the Libraries.

8114

#Done executing .. AFE77xx/bringup/devInit.py

#End Time 2022-11-10 13:16:09.507000

#Execution Time = 19.3180000782 s

#================ ERRORS:0, WARNINGS:0 ================#

#======

#Executing .. AFE77xx/bringup/basicBringup_Case-2.py

#Start Time 2022-11-10 13:16:20.725000

DONOT_OPEN_Afe77xxPG1p1_FULL - Device registers reset.

chipType: 0xa

chipId: 0x77

chipVersion: 0x11

2T2R1F Number: 0

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

2T2R1F Number: 1

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

LMK Clock Divider - Device registers reset.

lmk.writeReg(000,0x00000080)

lmk.writeReg(000,0x00000000)

LMK Clock Divider - Device registers reset.

lmk.writeReg(000,0x00000080)

lmk.writeReg(000,0x00000000)

lmk.writeReg(000,0x00000080)

lmk.writeReg(000,0x00000000)

lmk.writeReg(330,0x00000033)

lmk.writeReg(000,0x00000000)

lmk.writeReg(002,0x00000000)

lmk.writeReg(256,0x00000008)

lmk.writeReg(257,0x00000055)

lmk.writeReg(259,0x00000001)

lmk.writeReg(260,0x00000020)

lmk.writeReg(261,0x00000000)

lmk.writeReg(262,0x000000F0)

lmk.writeReg(263,0x00000044)

lmk.writeReg(264,0x00000066)

lmk.writeReg(265,0x00000055)

lmk.writeReg(267,0x00000001)

lmk.writeReg(268,0x00000020)

lmk.writeReg(269,0x00000000)

lmk.writeReg(270,0x000000F0)

lmk.writeReg(271,0x00000044)

lmk.writeReg(272,0x00000008)

lmk.writeReg(273,0x00000055)

lmk.writeReg(275,0x00000000)

lmk.writeReg(276,0x00000000)

lmk.writeReg(277,0x00000000)

lmk.writeReg(278,0x000000F9)

lmk.writeReg(279,0x00000000)

lmk.writeReg(280,0x00000018)

lmk.writeReg(281,0x00000055)

lmk.writeReg(283,0x00000000)

lmk.writeReg(284,0x00000020)

lmk.writeReg(285,0x00000000)

lmk.writeReg(286,0x000000F9)

lmk.writeReg(287,0x00000000)

lmk.writeReg(288,0x00000010)

lmk.writeReg(289,0x00000055)

lmk.writeReg(291,0x00000000)

lmk.writeReg(292,0x00000000)

lmk.writeReg(293,0x00000000)

lmk.writeReg(294,0x000000F9)

lmk.writeReg(295,0x00000011)

lmk.writeReg(296,0x00000008)

lmk.writeReg(297,0x00000055)

lmk.writeReg(299,0x00000000)

lmk.writeReg(300,0x00000000)

lmk.writeReg(301,0x00000000)

lmk.writeReg(302,0x000000F9)

lmk.writeReg(303,0x00000000)

lmk.writeReg(302,0x00000011)

lmk.writeReg(302,0x00000010)

lmk.writeReg(303,0x00000041)

lmk.writeReg(300,0x00000020)

lmk.writeReg(256,0x0000000C)

lmk.writeReg(256,0x0000000C)

lmk.writeReg(304,0x0000001E)

lmk.writeReg(305,0x00000055)

lmk.writeReg(307,0x00000000)

lmk.writeReg(308,0x00000020)

lmk.writeReg(309,0x00000000)

lmk.writeReg(310,0x000000F1)

lmk.writeReg(311,0x00000001)

lmk.writeReg(312,0x00000020)

lmk.writeReg(313,0x00000003)

lmk.writeReg(314,0x00000001)

lmk.writeReg(315,0x00000080)

lmk.writeReg(316,0x00000000)

lmk.writeReg(317,0x00000008)

lmk.writeReg(318,0x00000003)

lmk.writeReg(319,0x00000000)

lmk.writeReg(320,0x00000000)

lmk.writeReg(321,0x00000000)

lmk.writeReg(322,0x00000000)

lmk.writeReg(323,0x00000012)

lmk.writeReg(324,0x000000FF)

lmk.writeReg(325,0x00000000)

lmk.writeReg(326,0x00000010)

lmk.writeReg(327,0x0000001A)

lmk.writeReg(328,0x00000002)

lmk.writeReg(329,0x00000042)

lmk.writeReg(331,0x00000016)

lmk.writeReg(332,0x00000000)

lmk.writeReg(333,0x00000000)

lmk.writeReg(334,0x000000C0)

lmk.writeReg(335,0x0000007F)

lmk.writeReg(336,0x00000043)

lmk.writeReg(337,0x00000002)

lmk.writeReg(338,0x00000000)

lmk.writeReg(339,0x00000000)

lmk.writeReg(340,0x00000078)

lmk.writeReg(341,0x00000000)

lmk.writeReg(342,0x0000007D)

lmk.writeReg(343,0x00000000)

lmk.writeReg(344,0x00000096)

lmk.writeReg(345,0x00000006)

lmk.writeReg(346,0x00000000)

lmk.writeReg(347,0x000000D4)

lmk.writeReg(348,0x00000020)

lmk.writeReg(349,0x00000000)

lmk.writeReg(350,0x00000000)

lmk.writeReg(351,0x0000000B)

lmk.writeReg(352,0x00000000)

lmk.writeReg(353,0x00000001)

lmk.writeReg(354,0x00000044)

lmk.writeReg(355,0x00000000)

lmk.writeReg(356,0x00000000)

lmk.writeReg(357,0x0000000C)

lmk.writeReg(358,0x00000000)

lmk.writeReg(359,0x00000000)

lmk.writeReg(360,0x0000000C)

lmk.writeReg(361,0x00000059)

lmk.writeReg(362,0x00000020)

lmk.writeReg(363,0x00000000)

lmk.writeReg(364,0x00000000)

lmk.writeReg(365,0x00000000)

lmk.writeReg(366,0x00000013)

lmk.writeReg(380,0x00000015)

lmk.writeReg(381,0x0000000F)

Fuse farm load autoload done successful

No autload error

Purge

Purge

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

Purge

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

SPIA has got control of PLL pages

pll0: True; LO Frequency: 3500.01

pll1: True; LO Frequency: 2949.12

PLL Pages SPI control relinquished.

FB DSA 3.5G Band

RX HD3 default settings begins

RX HD3 default settings END

RX HD3 default dig-corr begins

delay(0.01)

delay(0.01)

RX HD3 default dig-corr ends

RX HD3 default settings begins

RX HD3 default settings END

RX HD3 default dig-corr begins

delay(0.01)

delay(0.01)

RX HD3 default dig-corr ends

Purge

Purge

Purge

*TX IQMC Patch Apply*

SPIA has got control of PLL pages

PLL Pages SPI control relinquished.

FW_VERSION=0x11119e

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

attack_value: 2899.74593284

decay_value: 1630.64697059

attack_value: 3650.5638426

decay_value: 1028.86868235

attack_value: 2899.74593284

decay_value: 1630.64697059

attack_value: 3650.5638426

decay_value: 1028.86868235

SPIA has got control of PLL pages

PLL Pages SPI control relinquished.

Sysref to RX AB, Read: 3; expected: 3

Sysref to RX CD, Read: 3; expected: 3

Sysref to FB A, Read: 1; expected: 1

Sysref to FB D, Read: 1; expected: 1

Sysref to TX AB, Read: 7; expected: 7

Sysref to TX CD, Read: 7; expected: 7

Digital Clock, Read: True; expected: 1

Sysref to Digital, Read: True; expected: 1

Sysref to Analog, Read: 7; expected: 7

Sysref Read as expected

###########Device DAC JESD-RX 0 Link Status###########

LOS Indicator for (Serdes Loss of signal) lane 0: 1

Frame Sync error (unexpected k28.5) for lane 0: 0

LOS Indicator for (Serdes Loss of signal) lane 1: 1

Frame Sync error (unexpected k28.5) for lane 1: 0

LOS Indicator for (Serdes Loss of signal) lane 2: 1

Frame Sync error (unexpected k28.5) for lane 2: 0

LOS Indicator for (Serdes Loss of signal) lane 3: 1

Frame Sync error (unexpected k28.5) for lane 3: 0

lane0 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state);

lane1 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state);

lane2 FIFO Errors=0b0000; Got errors:

lane3 FIFO Errors=0b0000; Got errors:

lane0 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane1 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane2 Errors=0b0000; Got errors:

lane3 Errors=0b0000; Got errors:

CS State TX0: 0b00001010 . It is expected to be 0b00001010

FS State TX0: 0b00000000 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 0; Alarms: 0xf0f00220f00L

###################################

###########Device DAC JESD-RX 1 Link Status###########

LOS Indicator for (Serdes Loss of signal) lane 0: 1

Frame Sync error (unexpected k28.5) for lane 0: 0

LOS Indicator for (Serdes Loss of signal) lane 1: 1

Frame Sync error (unexpected k28.5) for lane 1: 0

LOS Indicator for (Serdes Loss of signal) lane 2: 1

Frame Sync error (unexpected k28.5) for lane 2: 0

LOS Indicator for (Serdes Loss of signal) lane 3: 1

Frame Sync error (unexpected k28.5) for lane 3: 0

lane0 FIFO Errors=0b0001; Got errors: read_empty : FIFO is empty;

lane1 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state);

lane2 FIFO Errors=0b0000; Got errors:

lane3 FIFO Errors=0b0000; Got errors:

lane0 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane1 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane2 Errors=0b0000; Got errors:

lane3 Errors=0b0000; Got errors:

CS State TX0: 0b00001010 . It is expected to be 0b00001010

FS State TX0: 0b00000000 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 1; Alarms: 0xf0f00210f00L

###################################

SPIA has got control of PLL pages

PLL Pages SPI control relinquished.

#Done executing .. AFE77xx/bringup/basicBringup_Case-2.py

#End Time 2022-11-10 13:19:09.221000

#Execution Time = 168.496000051 s

#================ ERRORS:34, WARNINGS:8 ================#

Regards,

Soma

Hai Vijay,

I am also attaching the basicBringup_case2.py script that is updated and tested for loopback. kindly check this script.

I am not sure where the issue is

CODE :

'''

Latte Version: 2.13

Case RX TX FB CLK Notes

---- ----------------- ----------------- ----------------- ----------- ------------

1 245.76Msps, 24410 491.52Msps, 44210 491.52Msps, 22210 FS=2949.12M

SerDes=9830.4Mbps SerDes=9830.4Mbps SerDes=9830.4Mbps REF=491.52M

PLL0, LO=3500M PLL0, LO=3500M NCO=3500M

2 245.76Msps, 24410 245.76Msps, 24410 245.76Msps, 12410 FS=2949.12M

SerDes=9830.4Mbps SerDes=9830.4Mbps SerDes=9830.4Mbps REF=491.52M

PLL0, LO=3500M PLL0, LO=3500M NCO=3500M

3 245.76Msps, 24410 737.28Msps, 44210 737.28Msps, 22210 FS=2949.12M For HSDC RX ADC Capture, run "lmk.writeReg(256,0xc)" in Cmd Line

SerDes=9830.4Mbps SerDes=14745.6Mbps SerDes=14745.6Mbps REF=491.52M For HSDC FB ADC Capture & DAC Send, run "lmk.writeReg(256,0x8)" in Cmd Line

PLL0, LO=3500M PLL0, LO=3500M NCO=3500M

4 245.76Msps, 24410 491.52Msps, 44210 491.52Msps, 22210 FS=3317.76M

SerDes=9830.4Mbps SerDes=9830.4Mbps SerDes=9830.4Mbps REF=491.52M

PLL0, LO=2600M PLL0, LO=2600M NCO=2600M

'''

setupParams.selectedDut=1

if boardType in ("EVM","HSC1373"):

if setupParams.selectedDut==1:

AFE=AFE1

device=device1

logDumpInst=logDumpInst1

else:

AFE=AFE0

device=device0

logDumpInst=logDumpInst0

else:

setupParams.selectedDut=0

sysParams=AFE.systemParams

device.hardReadAlways=False

##### PLL & LO

sysParams.FRef = 491.52

sysParams.Fs = 2949.12

sysParams.pllMuxModes = 0

#0: 4T4R Mode with PLL0 as Master. PLL 0 for all the LOs.

#1: 4T4R Mode with PLL2 as Master. PLL 2 for all the LOs.

#2: 4T4R FDD Mode. PLL0 for TX and PLL2 for RX.

#3: 2*2T2R FDD Mode: PLL0 AB-TX;PLL3 AB-RX; PLL2 CD TX; PLL4 CD RX

#4: 2T2R FDD - TDD Mode: PLL0 AB-TX; PLL3-AB-RX; PLL2 CD

sysParams.pllLo = [3500.01,sysParams.Fs,3501.06,1800.24,3400.0] #PLL Frequencies for PLLs [0,1,2,3,4]

sysParams.setTxLoFbNcoFreqForTxCalib = True

## In below parameters, first in the array is for first 2T2R1F and second 2T2R1F.

# JESD and Serdes Parameters

sysParams.useSpiSysref = False

sysParams.LMFSHdRx = ["24410","24410"]

sysParams.LMFSHdFb = ["12410","12410"]

sysParams.LMFSHdTx = ["24410","24410"]

sysParams.systemMode = [1,1] # 0-Identical, 1-FDD, 2-TDD

sysParams.dedicatedLaneMode = [1,1]

sysParams.jesdProtocol = 0#1#0 # -0:B; 1:H; 2:C

sysParams.serdesFirmware = True

sysParams.jesdTxLaneMux = [0,1,4,5,2,3,6,7] # RX1,RX2,RX3,RX4,FB1,FB2

sysParams.jesdRxLaneMux = [0,1,2,3,4,5,6,7]

sysParams.jesdRxRbd = [15, 15]

sysParams.jesdScr = [True,True]

sysParams.serdesTxLanePolarity = [False,False,False,False,True,True,True,True]

sysParams.serdesRxLanePolarity = [False,False,False,False,True,True,True,True]

sysParams.jesdK = [16,16]

sysParams.syncLoopBack = True

sysParams.jesdLoopbackEn = 1

sysParams.jesdTxRxABSyncMux = 0

sysParams.jesdTxRxCDSyncMux = 0

sysParams.jesdTxFBABSyncMux = 0

sysParams.jesdTxFBCDSyncMux = 0

sysParams.jesdRxABSyncMux = 0

sysParams.jesdRxCDSyncMux = 0

sysParams.jesdABLvdsSync = 1

sysParams.jesdCDLvdsSync = 1

# Decimation and interpolation Parameters

sysParams.ddcFactorRx = [12,12]

sysParams.ddcFactorFb = [12,12]

sysParams.ducFactorTx = [12,12]

sysParams.fbNco = [3500.01,3500.01]

sysParams.lowIfNcoRx = [0,0]

sysParams.lowIfNcoTx = [0,0]

sysParams.lowIfNcoFb = [0,0]

LMKParams.pllEn = True

LMKParams.lmkFrefClk = True

#LMKParams.inputClk = 1474.56

LMKParams.sysrefFreq = 7.68

if simulationMode==False:

setupParams.skipFpga=1

setupParams.skipLmk=0

AFE.skipRxConfig=0

AFE.skipFbConfig=0

AFE.skipTxConfig=0

AFE.skipAgc=0

sysParams.gpioConfigMode=1

'''

#PAP Config

sysParams.txDsaUpdateMode=1

for i in range(4):

sysParams.srConfigParams[i]['GainStepSize']=38

sysParams.srConfigParams[i]['AttnStepSize']=38

sysParams.srConfigParams[i]['AmplUpdateCycles']=6

sysParams.srConfigParams[i]['threshold']=30

sysParams.srConfigParams[i]['enable']=True

sysParams.srConfigParams[i]['mode']=10

#Ext AGC Config

for i in range(4):

sysParams.agcRegConfigParams[i]['enableIa']=0

sysParams.agcRegConfigParams[i]['phmOvrEn']=1

sysParams.agcRegConfigParams[i]['enableSa']=0

sysParams.agcRegConfigParams[i]['enableSd']=0

sysParams.agcRegConfigParams[i]['enableBa']=1

sysParams.agcRegConfigParams[i]['gainControl']=4

sysParams.agcRegConfigParams[i]['fdsaOffset']=6

#INT Pins

sysParams.intPinsParams[0]['JESD']=True

sysParams.intPinsParams[0]['SPI']=True

sysParams.intPinsParams[0]['SRTXA']=True

sysParams.intPinsParams[0]['SRTXB']=True

sysParams.intPinsParams[0]['SRTXC']=True

sysParams.intPinsParams[0]['SRTXD']=True

sysParams.intPinsParams[0]['PLL0']=True

sysParams.intPinsParams[0]['PLL1']=True

sysParams.intPinsParams[0]['PLL2']=True

sysParams.intPinsParams[0]['PLL3']=True

sysParams.intPinsParams[0]['PLL4']=True

'''

#Calibrations

sysParams.enableRxDsaFactoryCal = False

sysParams.enableTxDsaFactoryCal = False

sysParams.enableTxIqmcLolTrackingCorr = True

sysParams.enableRxIqmcLolTrackingCorr = True

sysParams.txIqMcCalibMode = 0 # 0 -Single Fb Mode FB AB ; 1 -Single Fb Mode FB CD ; 2- Dual Fb_Mode

sysParams.txDsaCalibMode = 0

sysParams.rxDsaCalibMode = 0

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\config.txt")

logDumpInst.logFormat=0x4

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.rewriteFile=1

device.rawWriteLogsFile=ASTERIX_DIR+DEVICES_DIR+r"\test.txt"#"D:\AFE77xx_config/testBroadcast.txt"

lmk.rawWriteLogEn=0

lmk.rawWriteLogsFile=device.rawWriteLogsFile

# AFE.initializeConfig()

AFE.deviceBringup()

device.rawWriteLogEn=1

lmk.rawWriteLogEn=0

engine.sampleNo=32768

AFE.TOP.overrideTdd(1, 1, 1)

Regards,

Soma

Hai Vijay,

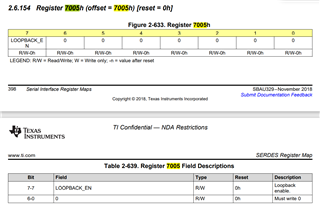

As I changed the parameter sysParams.jesdLoopbackEn = 1, how can I say this parameter is configured correctly? I also verified the latte.exe log to check this loopback register is configured are not, as per the sbau329_AFE77XX_TRM register detail document page no 398 says that loopback enable register is 0x7005. This register is not configured when I run this basicBringup_case2.py script.

I don't know that this is the correct register I am looking at. Kindly confirm me that how to check this sysParams.jesdLoopbackEn = 1 is correctly set.

While testing I have observed that some status led’s on board. PLL2 Locked led is high and LMK Locked is low, STAT 0 is low and STAT 1 is low.

Kindly check the previous comments also, I am also debugging on my side.

waiting for your reply

Thanks in advance

Regards

Soma

Hai Vijay,

May I know any update on this. We are waiting for your reply

Regards

Soma

Hi Soma,

I have verified the bringup script at this link for repeater mode:

https://tidrive.ext.ti.com/u/ukpb6n1KW8SoSlvs/1f71e9c4-adc1-4b24-aea8-dda775ccca17?l

There are some expected errors in log when this script is run. I have included the log file in the same folder.

PLL2 Locked led is high and LMK Locked is low, STAT 0 is low and STAT 1 is low.

This LED status is expected.

Regards,

Vijay

Hai Vijay,

Thanks for reply.

What is this repeater mode ? How it works ?

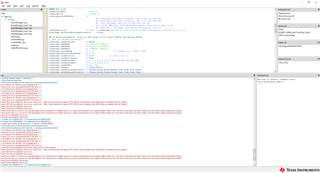

I downloaded the script from the link and ran the script, still I have errors in the log same as you said. I observed that there are many difference in the log that you sent and that I ran. I also attaching the log which I have ran in my PC.

Vijay, My request is there any possible to have video call between us, to get solved this very clearly and I it will be more easy to see my test setup also. I am very new to this board. I need your help. kindly give some positive reply for this.

Regards

Soma

LOG WINDOW :

#======

#Executing .. AFE77xx/bringup/setup.py

#Start Time 2022-11-17 09:29:31.062000

AFE77xxLibraryPG1P1

spi - USB Instrument created.

resetDevice

Purge

MPSSE mode set

Kintex RegProgrammer - USB Instrument created.

Kintex RegProgrammer - USB Instrument created.

#Done executing .. AFE77xx/bringup/setup.py

#End Time 2022-11-17 09:29:37.328000

#Execution Time = 6.26600003242 s

#================ ERRORS:0, WARNINGS:0 ================#

#======

#Executing .. AFE77xx/bringup/devInit.py

#Start Time 2022-11-17 09:29:47.731000

Successfully Loaded the Libraries.

8114

#Done executing .. AFE77xx/bringup/devInit.py

#End Time 2022-11-17 09:30:06.797000

#Execution Time = 19.0659999847 s

#================ ERRORS:0, WARNINGS:0 ================#

#======

#Executing .. AFE77xx/bringup/script11.py

#Start Time 2022-11-17 09:30:14.609000

DONOT_OPEN_Afe77xxPG1p1_FULL - Device registers reset.

chipType: 0xa

chipId: 0x77

chipVersion: 0x11

2T2R1F Number: 0

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

2T2R1F Number: 1

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

LMK Clock Divider - Device registers reset.

lmk.writeReg(000,0x00000080)

lmk.writeReg(000,0x00000000)

LMK Clock Divider - Device registers reset.

lmk.writeReg(000,0x00000080)

lmk.writeReg(000,0x00000000)

lmk.writeReg(000,0x00000080)

lmk.writeReg(000,0x00000000)

lmk.writeReg(330,0x00000033)

lmk.writeReg(000,0x00000000)

lmk.writeReg(002,0x00000000)

lmk.writeReg(256,0x00000008)

lmk.writeReg(257,0x00000055)

lmk.writeReg(259,0x00000001)

lmk.writeReg(260,0x00000020)

lmk.writeReg(261,0x00000000)

lmk.writeReg(262,0x000000F0)

lmk.writeReg(263,0x00000044)

lmk.writeReg(264,0x00000066)

lmk.writeReg(265,0x00000055)

lmk.writeReg(267,0x00000001)

lmk.writeReg(268,0x00000020)

lmk.writeReg(269,0x00000000)

lmk.writeReg(270,0x000000F0)

lmk.writeReg(271,0x00000044)

lmk.writeReg(272,0x00000008)

lmk.writeReg(273,0x00000055)

lmk.writeReg(275,0x00000000)

lmk.writeReg(276,0x00000000)

lmk.writeReg(277,0x00000000)

lmk.writeReg(278,0x000000F9)

lmk.writeReg(279,0x00000000)

lmk.writeReg(280,0x00000018)

lmk.writeReg(281,0x00000055)

lmk.writeReg(283,0x00000000)

lmk.writeReg(284,0x00000020)

lmk.writeReg(285,0x00000000)

lmk.writeReg(286,0x000000F9)

lmk.writeReg(287,0x00000000)

lmk.writeReg(288,0x00000010)

lmk.writeReg(289,0x00000055)

lmk.writeReg(291,0x00000000)

lmk.writeReg(292,0x00000000)

lmk.writeReg(293,0x00000000)

lmk.writeReg(294,0x000000F9)

lmk.writeReg(295,0x00000011)

lmk.writeReg(296,0x00000008)

lmk.writeReg(297,0x00000055)

lmk.writeReg(299,0x00000000)

lmk.writeReg(300,0x00000000)

lmk.writeReg(301,0x00000000)

lmk.writeReg(302,0x000000F9)

lmk.writeReg(303,0x00000000)

lmk.writeReg(302,0x00000011)

lmk.writeReg(302,0x00000010)

lmk.writeReg(303,0x00000041)

lmk.writeReg(300,0x00000020)

lmk.writeReg(256,0x0000000C)

lmk.writeReg(256,0x0000000C)

lmk.writeReg(304,0x0000001E)

lmk.writeReg(305,0x00000055)

lmk.writeReg(307,0x00000000)

lmk.writeReg(308,0x00000020)

lmk.writeReg(309,0x00000000)

lmk.writeReg(310,0x000000F1)

lmk.writeReg(311,0x00000001)

lmk.writeReg(312,0x00000020)

lmk.writeReg(313,0x00000003)

lmk.writeReg(314,0x00000001)

lmk.writeReg(315,0x00000080)

lmk.writeReg(316,0x00000000)

lmk.writeReg(317,0x00000008)

lmk.writeReg(318,0x00000003)

lmk.writeReg(319,0x00000000)

lmk.writeReg(320,0x00000000)

lmk.writeReg(321,0x00000000)

lmk.writeReg(322,0x00000000)

lmk.writeReg(323,0x00000012)

lmk.writeReg(324,0x000000FF)

lmk.writeReg(325,0x00000000)

lmk.writeReg(326,0x00000010)

lmk.writeReg(327,0x0000001A)

lmk.writeReg(328,0x00000002)

lmk.writeReg(329,0x00000042)

lmk.writeReg(331,0x00000016)

lmk.writeReg(332,0x00000000)

lmk.writeReg(333,0x00000000)

lmk.writeReg(334,0x000000C0)

lmk.writeReg(335,0x0000007F)

lmk.writeReg(336,0x00000043)

lmk.writeReg(337,0x00000002)

lmk.writeReg(338,0x00000000)

lmk.writeReg(339,0x00000000)

lmk.writeReg(340,0x00000078)

lmk.writeReg(341,0x00000000)

lmk.writeReg(342,0x0000007D)

lmk.writeReg(343,0x00000000)

lmk.writeReg(344,0x00000096)

lmk.writeReg(345,0x00000006)

lmk.writeReg(346,0x00000000)

lmk.writeReg(347,0x000000D4)

lmk.writeReg(348,0x00000020)

lmk.writeReg(349,0x00000000)

lmk.writeReg(350,0x00000000)

lmk.writeReg(351,0x0000000B)

lmk.writeReg(352,0x00000000)

lmk.writeReg(353,0x00000001)

lmk.writeReg(354,0x00000044)

lmk.writeReg(355,0x00000000)

lmk.writeReg(356,0x00000000)

lmk.writeReg(357,0x0000000C)

lmk.writeReg(358,0x00000000)

lmk.writeReg(359,0x00000000)

lmk.writeReg(360,0x0000000C)

lmk.writeReg(361,0x00000059)

lmk.writeReg(362,0x00000020)

lmk.writeReg(363,0x00000000)

lmk.writeReg(364,0x00000000)

lmk.writeReg(365,0x00000000)

lmk.writeReg(366,0x00000013)

lmk.writeReg(380,0x00000015)

lmk.writeReg(381,0x0000000F)

Fuse farm load autoload done successful

No autload error

Purge

Purge

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

Purge

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

SPIA has got control of PLL pages

pll0: True; LO Frequency: 2600.0

pll1: True; LO Frequency: 2949.12

PLL Pages SPI control relinquished.

FB DSA 2.6G Band

RX HD3 default settings begins

RX HD3 default settings END

RX HD3 default dig-corr begins

delay(0.01)

delay(0.01)

RX HD3 default dig-corr ends

RX HD3 default settings begins

RX HD3 default settings END

RX HD3 default dig-corr begins

delay(0.01)

delay(0.01)

RX HD3 default dig-corr ends

Purge

Purge

Purge

*TX IQMC Patch Apply*

SPIA has got control of PLL pages

PLL Pages SPI control relinquished.

FW_VERSION=0x11119e

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

MACRO_READY: True

MACRO_ACK: True

MACRO_DONE: True

MACRO_ERROR: False

SPIA has got control of PLL pages

PLL Pages SPI control relinquished.

Sysref to RX AB, Read: 3; expected: 3

Sysref to RX CD, Read: 3; expected: 3

Sysref to FB A, Read: 1; expected: 1

Sysref to FB D, Read: 1; expected: 1

Sysref to TX AB, Read: 7; expected: 7

Sysref to TX CD, Read: 7; expected: 7

Digital Clock, Read: True; expected: 1

Sysref to Digital, Read: True; expected: 1

Sysref to Analog, Read: 7; expected: 7

Sysref Read as expected

###########Device DAC JESD-RX 0 Link Status###########

LOS Indicator for (Serdes Loss of signal) lane 0: 1

Frame Sync error (unexpected k28.5) for lane 0: 0

LOS Indicator for (Serdes Loss of signal) lane 1: 1

Frame Sync error (unexpected k28.5) for lane 1: 0

LOS Indicator for (Serdes Loss of signal) lane 2: 1

Frame Sync error (unexpected k28.5) for lane 2: 0

LOS Indicator for (Serdes Loss of signal) lane 3: 1

Frame Sync error (unexpected k28.5) for lane 3: 0

lane0 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state);

lane1 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state);

lane2 FIFO Errors=0b0000; Got errors:

lane3 FIFO Errors=0b0000; Got errors:

lane0 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane1 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane2 Errors=0b0000; Got errors:

lane3 Errors=0b0000; Got errors:

CS State TX0: 0b00001000 . It is expected to be 0b00001010

FS State TX0: 0b00000000 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 0; Alarms: 0xf0f00220f00L

###################################

###########Device DAC JESD-RX 1 Link Status###########

LOS Indicator for (Serdes Loss of signal) lane 0: 1

Frame Sync error (unexpected k28.5) for lane 0: 0

LOS Indicator for (Serdes Loss of signal) lane 1: 1

Frame Sync error (unexpected k28.5) for lane 1: 0

LOS Indicator for (Serdes Loss of signal) lane 2: 1

Frame Sync error (unexpected k28.5) for lane 2: 0

LOS Indicator for (Serdes Loss of signal) lane 3: 1

Frame Sync error (unexpected k28.5) for lane 3: 0

lane0 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state);

lane1 FIFO Errors=0b0010; Got errors: read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialized with init_state);

lane2 FIFO Errors=0b0000; Got errors:

lane3 FIFO Errors=0b0000; Got errors:

lane0 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane1 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane2 Errors=0b0000; Got errors:

lane3 Errors=0b0000; Got errors:

CS State TX0: 0b00001010 . It is expected to be 0b00001010

FS State TX0: 0b00000000 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 1; Alarms: 0xf0f00220f00L

###################################

SPIA has got control of PLL pages

PLL Pages SPI control relinquished.

###########Device DAC JESD-RX 0 Link Status###########

LOS Indicator for (Serdes Loss of signal) lane 0: 1

Frame Sync error (unexpected k28.5) for lane 0: 0

LOS Indicator for (Serdes Loss of signal) lane 1: 1

Frame Sync error (unexpected k28.5) for lane 1: 0

LOS Indicator for (Serdes Loss of signal) lane 2: 1

Frame Sync error (unexpected k28.5) for lane 2: 0

LOS Indicator for (Serdes Loss of signal) lane 3: 1

Frame Sync error (unexpected k28.5) for lane 3: 0

lane0 Errors=0b0111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error;

lane1 Errors=0b0111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error;

lane2 Errors=0b0000; Got errors:

lane3 Errors=0b0000; Got errors:

CS State TX0: 0b00000000 . It is expected to be 0b00001010

FS State TX0: 0b00000000 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 0; Alarms: 0x70700000f00L

###################################

###########Device DAC JESD-RX 1 Link Status###########

LOS Indicator for (Serdes Loss of signal) lane 0: 1

Frame Sync error (unexpected k28.5) for lane 0: 0

LOS Indicator for (Serdes Loss of signal) lane 1: 1

Frame Sync error (unexpected k28.5) for lane 1: 0

LOS Indicator for (Serdes Loss of signal) lane 2: 1

Frame Sync error (unexpected k28.5) for lane 2: 0

LOS Indicator for (Serdes Loss of signal) lane 3: 1

Frame Sync error (unexpected k28.5) for lane 3: 0

CS State TX0: 0b00001010 . It is expected to be 0b00001010

FS State TX0: 0b00000101 . It is expected to be 0b00000101

Couldn't get the link up for device RX: 1; Alarms: 0xf00

###################################

#Done executing .. AFE77xx/bringup/script11.py

#End Time 2022-11-17 09:31:19.439000

#Execution Time = 64.8299999237 s

#================ ERRORS:56, WARNINGS:8 ================#

Hi Soma,

JESD loopback mode is called repeater mode as the ADC input is "repeated" as DAC output in this mode.

Please follow below instructions and you should see the expected output as I outlined below:

Hardware connections:

1. Connect a 6V power supply to AFE7700EVM with current limit set to 5A. The voltage and current limit must not be lower than these values.

2. Connect the USB port of AFE7700EVM to PC.

Software installation:

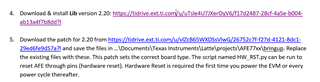

1. Install AFE77xx_EVM_GUI_v2p13p1.exe from secure folder.

2. Follow steps 4 and 5 from Latte_Upgrade_Instructions.docx in secure folder to update to latest version and add needed scripts.

3. Copy the script from this link: https://tidrive.ext.ti.com/u/ukpb6n1KW8SoSlvs/1f71e9c4-adc1-4b24-aea8-dda775ccca17?l to …\Documents\Texas Instruments\Latte\projects\AFE77xx\bringup folder in your PC.

Configuring the AFE7700EVM:

1. Open latte and run setup.py, devInit.py, HW_RST.py and Bringup_repeaterMode.py resepctively.

2. At the end of the log, you should get expected CS and FS state as below for both DAC JESD-RX 0 and DAC JESD-RX 1 link Status:

CS State TX0: 0b00001010 . It is expected to be 0b00001010

FS State TX0: 0b00000101 . It is expected to be 0b00000101

Other JESD errors can be ignored.

Testing functionality:

1. Connect an RF signal generator to RX1 input. Set frequency to 2.61GHz and amplitude to -10dBm.

2. Connect a spectrum analyzer to TX1 output. You should see output tone at 2.61GHz.

3. You can test all the other 3 RX and TX pairs the same way.

In case you don't get this expected output, I will contact you via email directly and we can discuss how to debug and have a call if needed.

Regards,

Vijay

Hai Vijay,

Thanks for the valuable reply.

Software installation :

I installed the software AFE77xx_EVM_GUI_v2p13p1.exe from the is path "C:\Users\X54818\Desktop\TV2D\AFE7700\AFE7700".

As you said I am trying to do step 4 and step 5 from the Latte_Upgrade_Instructions.docx, but the link page is showing me "Could not find shared item. It has been either moved or deleted, or the link has expired". Can you please send me the correct link.

Regards

Soma

Soma,

I sent you an email with updated links. I apologize for the issue with these links.

Regards,

Vijay