Other Parts Discussed in Thread: AFE7901, AFE7900

Hi,

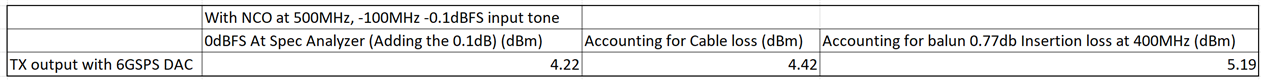

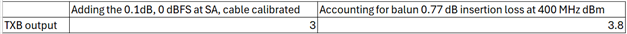

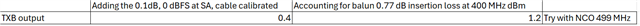

According to the datasheet, the AFE7901 TX output is 5.7 dBm for full scale diginal input.

However when we measured our own design, there were several dB missing.

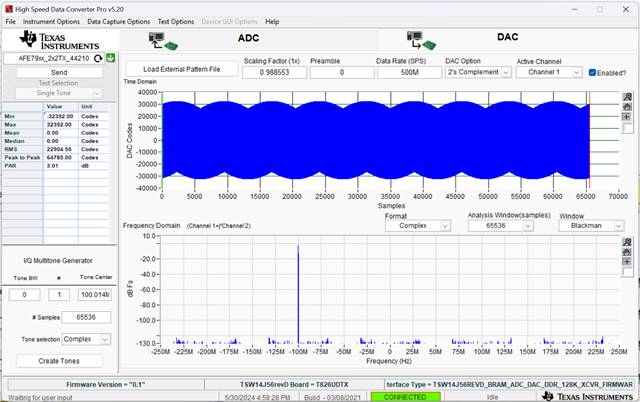

The AFE7900 EVM also shows the same result. With the digital signal of scale factor 1 generated in High Speed Data pro, the level of TXB output signal at around 500 MHz is only 1 dBm.

Could you please advise?

Best regards

Yinan Zhang