Other Parts Discussed in Thread: AFE4300

Hi All,

I am working on interfacing AFE4300 (using PDK for evaluation for now) with Mediatek IOT Chipset 76x7 over SPI. The basic problem i am facing is i am not able to read the registers and RDY pin is not getting low to let me read the adc data register.

Below is brief summary of what i have done so far.

A. Power [J102 connector of PDK]:-

I am using MMB3 board for powering up the AFE4300 PDK and connected Mediatek Chipset over SPI. Before this i ensured that the PDK is working with provided GUI application from TI.

B. SPI Connections [J103 connector of PDK ]:-

1. SPI CLK :- 2MHz (as it is used in AFE4300 PDK)

2. RDY :- Input gpio pin (which is always showing high)

3. RST :- Output gpio pin (working just fine)

4. MOSI :- I can see data on this line.

5. MISO :- It is low by default but when write is perform or read is perform during that it becomes high so the output is always (0xffff)

6. STE :- Working just fine as expected to be low during accessing AFE4300 over SPI.

7. AFE CLK :- 1MHz as suggested in the datasheet.

8. GND :- connected to Mediatek Chipset Dev Board ground pin

C. SPI Configurations for SPI controller in Mediatek (using HAL SPI driver provided in Mediatek LinkitSDK 4.5.1v public for 76x7):-

1. MSB Bit first.

2. SPI CLK -> 2MHz

3. CLK Phase = 1

4. CLK Polarity = 0

D. SW Driver and Testing :-

I am able to see over logic analyzer whatever data i am trying to write.

To start with the initialization, i have configured afe4300 registers with the following values :-

write_reg(REG_ADC_CTRL1,0x5140);

write_reg(REG_MISC_R1,0x0000);

write_reg(REG_MISC_R2,0xFFFF);

write_reg(REG_DEV_CTRL1,0x0004); //Power down both signal chains

write_reg(REG_ISW_MUX,0x0000);

write_reg(REG_VSEN_MUX,0x0000);

write_reg(REG_IQ_MODE,0x0000);

write_reg(REG_WS_CTRL,0x0000);

write_reg(REG_BCM_DAC_FREQ,0x0040);

write_reg(REG_DEV_CTRL2,0x0000);

write_reg(REG_ADC_CTRL2,0x0011);

write_reg(REG_MISC_R3,0x00C0);

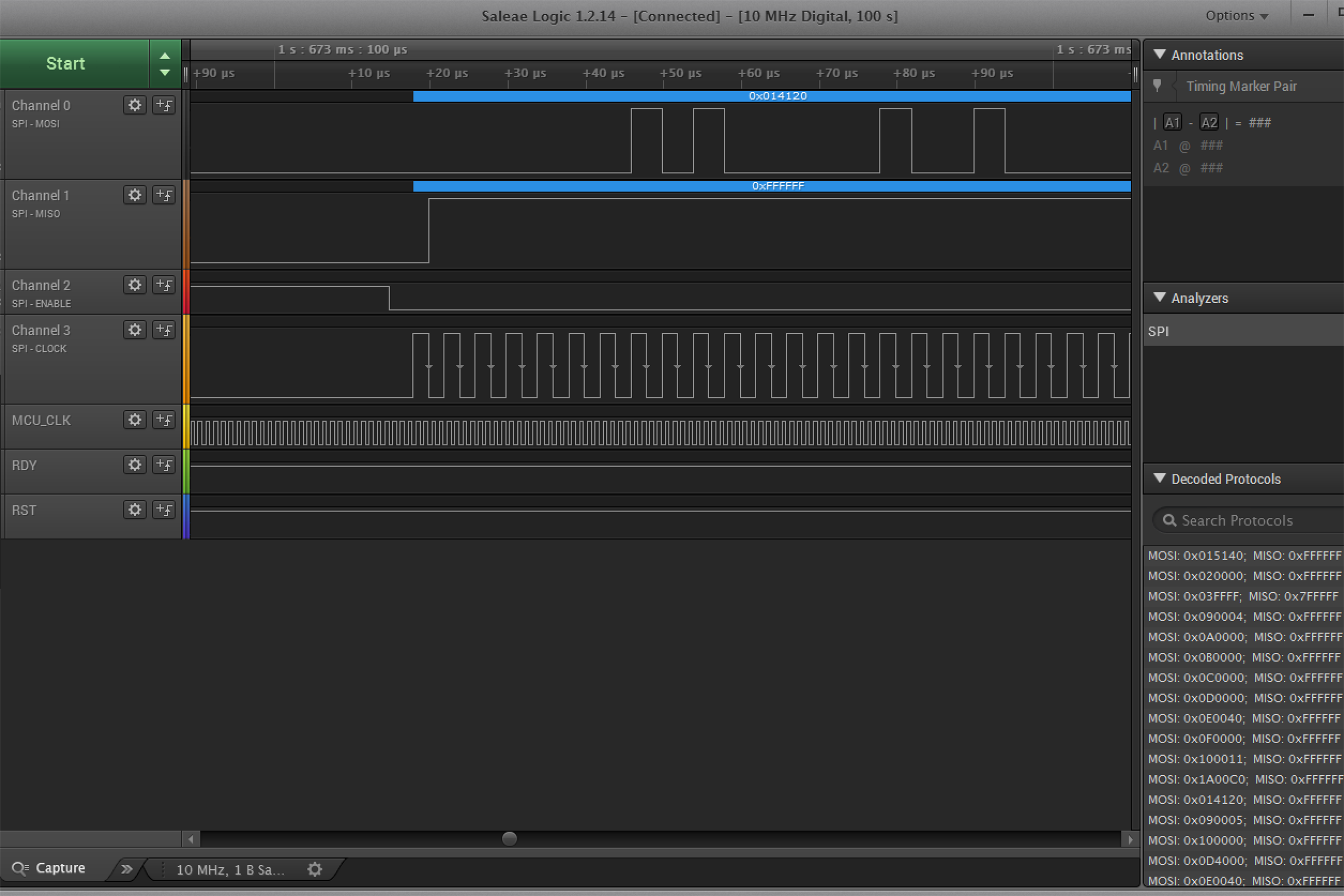

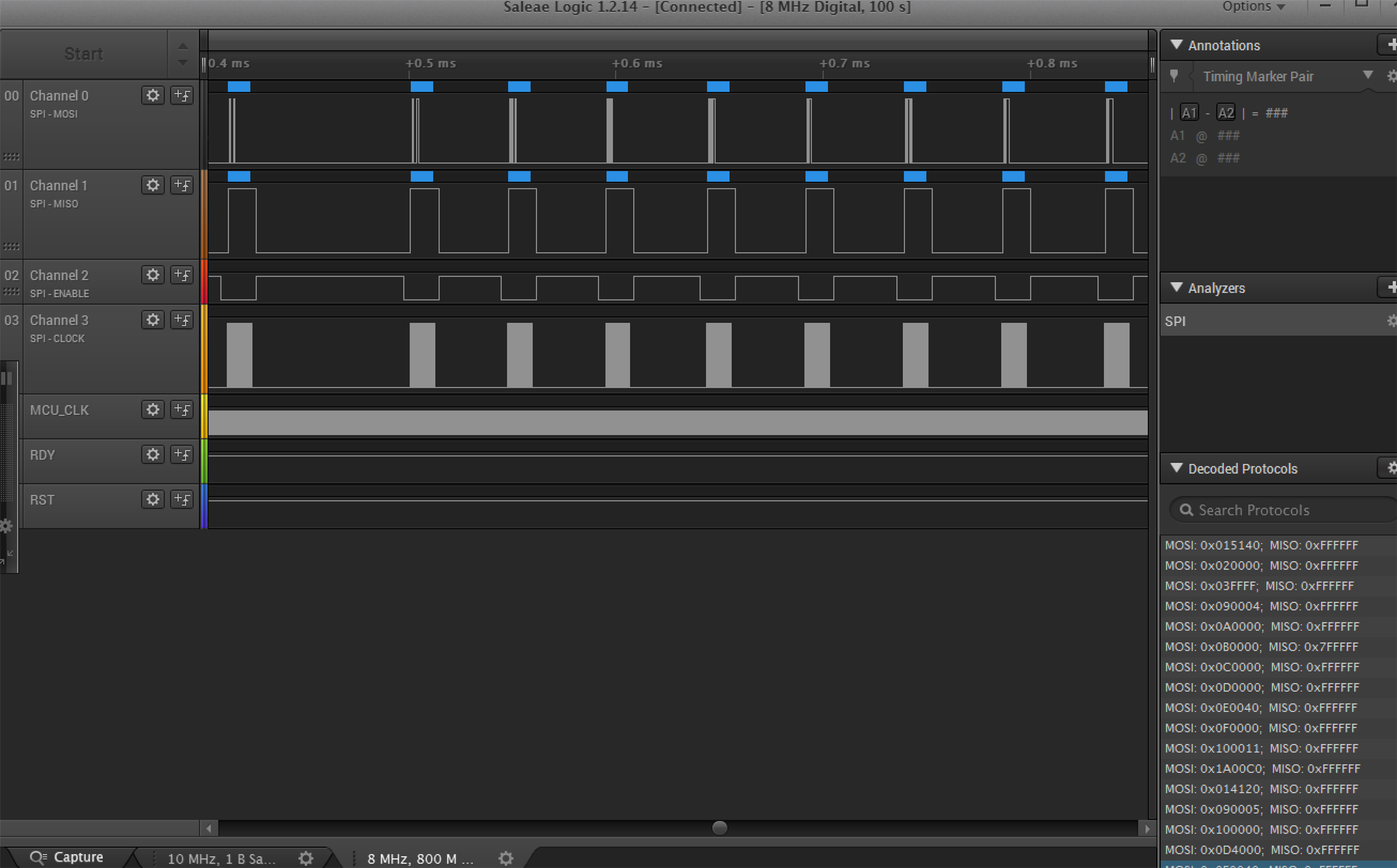

Below is the output of logic analyzer :-

But when i am trying to read the same register it is always as shown in the logic analyzer. Also , when i am trying to read the ADC register for weight measurements after configuring as below mentioned. The ready pin is not changing its state to low.

Configuring for Weight Scale Measurements :-

write_reg(REG_ADC_CTRL1,0x4120); //Differential measurement mode, 32 SPS

write_reg(REG_DEV_CTRL1,0x0005); //Power up weigh scale signal chain

write_reg(REG_ADC_CTRL2,0x0000); //ADC selects output of weigh scale

write_reg(REG_WS_CTRL,WS_CTRL_PGA_GAIN(DAC_GAIN_3)); //Gain = 3 DAC Offset = -1

write_reg(REG_BCM_DAC_FREQ,0x0040); //Frequency = default

write_reg(REG_IQ_MODE,0x0000); //Disable IQ mode

write_reg(REG_ISW_MUX,0x0000); //Channels IOUTP1 and IOUTN0

write_reg(REG_VSEN_MUX,0x0000); //Channels VSENSEP1 and VSENSEN0

I have followed couple of related issues posted in the E2E forum too.

I would request for help and guidance in this.

Appreciate your help in advance

Thank You

Regards,

Nitish