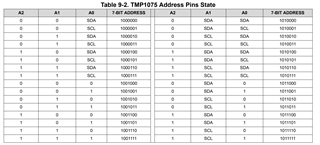

Can someone please clarify how the device address config works when connectin A0 or A1 to SCL or SDA? I see the datasheet states that the address is sampled on every bus communication, during which, the state of SCL and SDA change. It's not clear how this works reliably on every communication, and also how this differs from connection to V+ or GND. One thought was that it sensed a START condition, and sampled pins at that time. However, in START condition, SDA = LOW, and SCL = HIGH.... how is it differentiated from GND and V+? A clearer explanation would be helpful. Thank you.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.