Hello,

There are some questions about AFE3010:

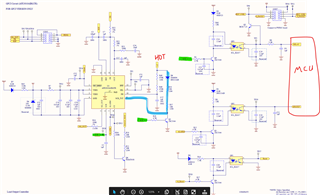

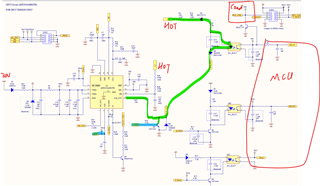

1. SCR (Pin 6):

- What is the output voltage range ? What is the factor affecting the output voltage?

- What is the duration (ms) of the output inrush pulse? What is factor affecting the duration?

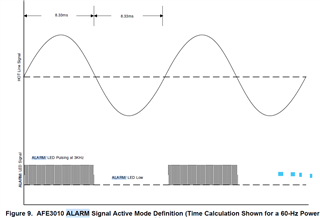

2. ALARM (Pin 7):

- If there is current leakage detected, the function “Self-Test” will stop?

- If there is current leakage detected, the “ALARM” pin will keep as below capture? Any method to resume “ALARM” pin to logic LOW except re-power up?

3. SCR_TST (Pin 9):

- According to datasheet application circuitry recommended to use 51kR, 1% for R11. If our product application with power supply 120Vac, 60Hz or 240V,60Hz, what is the recommended value and tolerance for R11?

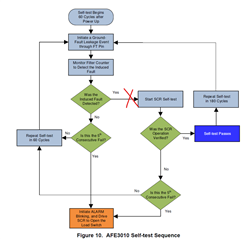

4. Datasheet : "7.3.7 Self-test function" : The AFE3010 performs two different types of self-test : periodic self-test and continuous self-test

- For the “Periodic Self-Test” block diagram, should we refer to “Figure 10”?

- For the “Periodic Self-Test” block diagram, should we refer to “Figure 10”?

5. Datasheet :

- Any requirement for VDD rising time? (i.e. the VDD rising time should be faster than specific IO?)