Other Parts Discussed in Thread: TMAG5170

Hi,

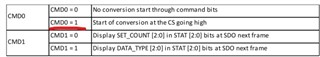

I have problem with the SET_COUNT value on the MISO line when starting a conversion via "CS going high" command.

According to the datahseet TMAG5170 shall start the conversion, when CS goes high.

I noticed, that SET_COUNT is incremented more than once, when CS is in low state for a long time.

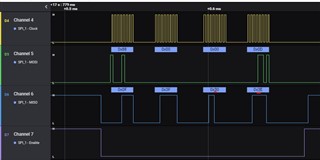

My current sequence to start the conversion is as follows:

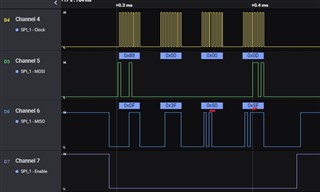

- reading from 0x08 - CONV_STATUS register (I need information about SET_COUT, here it is equal 0x03),

- writting to 0x00 - DEVICE_CONFIG register (trigger conversion, CMD0=1, here CS pin in low state is intentionally ~750us ),

- reading from 0x08 - CONV_STATUS register (I compare SET_COUT values - before and after conversion, here it is equal 0x05).

SPI bus log:

SET_COUT is equal 0x05 insted of 0x04 in second 0x08 register readout.

My configuration during initialization:

- 0x00 register = 0x213A (OPERATING_MODE = 0x03 - Active trigger mode, CONV_AVG = 0x02 - oversampling 4x),

- 0x01 register = 0x81C0,

- 0x02 register = 0x0020 (TRIGGER_MODE = 0x00 - Conversion start at SPI command),

- 0x03 register = 0x0000.

I suppose the conversion is started by TMAG5170 when 4th byte is received, and second conversion is started, because CS pin is low.

When during writing to 0x00 register:

- oversampling is equal to x8, the counter is increased by 1, which is the correct behaviour (TMAG conversion is longer),

- low state of the CS pin is shorter (e. g. ~650us), then counter is increased by 1, so correct behaviour,

- low state of the CS pin is longer (e. g. ~1650us), then counter is increased by 3, so incorrect behaviour (in my opinion).

So, I have a question: is the behavior of TMAG5170 correct?