Hi,

We have designed GFCI Circuit for our EV charger product & the AC power input t is 208/240VAC 60Hz [L1 to L2] US region.

We have set the Trip current value to 18-20mArms & we have been facing issue that the Trip current is not stable at change in Supply voltage. The trip current keeps varying when the AC voltage is varied.

Ex: Trip current set to 18mArms at 240VAC trips at 14mArms at 208VAC.

We have following Questions,

1. Will the Chip work for 208 to 240VAC 60Hz ? The datasheet mentions it Supports 120-V/ 60-Hz or 220-V/ 50-Hz systems.

2. Will the Chip work on 20VDC Power supply [VDD1 & VDD2]? Instead of powering it from AC followed by Bridge rectifier ? We tried to power it up from 20VDC power supply but the Self test fails.

3. What is the voltage of VTH:1-4 ?

4. Since the System works on L1 to L2 208/240VAC, Adding the current limiting resistor [R177] at the L2, fails the circuit. Does the Current limiting resistor not needed on L2 line ?

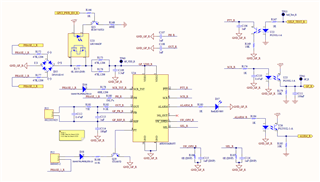

Below is our Schematics, We have been working on to tune the Burden resistor & Trip current value [R181 & R182 respectively].