Other Parts Discussed in Thread: 66AK2G12,

Tool/software: Code Composer Studio

To whom it may concern,

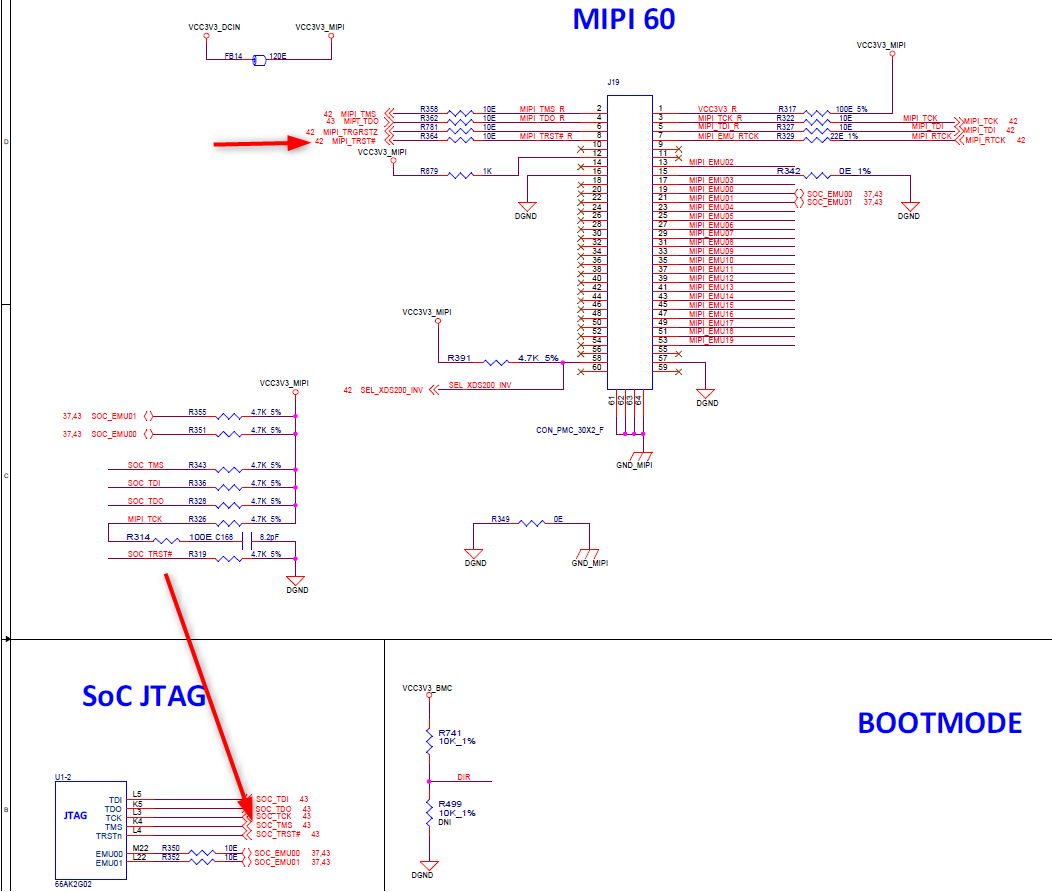

Following is the schematic of JTAG connection on our prototype board. After several modification of the prototype board, we still couldn't pass the CCS "test connection". Is there any similar design that we can use as a reference?

The hardware changes we've made are:

(1) make the TRSTN on K2G "high"

(2) connect the nRESET pin of XDS200 to "high" (doesn't change anything in the CCS error message)

(3) connect the TDIS (GND) pin of XDS200 to GND (change CCS error message from -183 to -233)

For the XDS200 pin definition please refer to http://support.spectrumdigital.com/ccs53/xds2xx/files/xds200_quickstart_guide.pdf

When using CCS "test connection" I chose "Texas Instruments XDS2xx USB Debug Probe" for "Connection", and "66AK2G12" for "Board or Device". The CCS version is 8.0.0.00016.

We've checked this "Debugging JTAG" manual: http://software-dl.ti.com/ccs/esd/documents/ccsv7_debugging_jtag_connectivity_issues.html

And the "XDS Target Connection Guide - Design guidelines for JTAG": http://dev.ti.com/tirex/#/?link=Development%20Tools%2FDebug%20Probes%2FXDS%2FDocuments%2FXDS%20Target%20Connection%20Guide

We also tried to connect the XDS200 to "CPLD JTAG" on K2G EVM board with the same 6 pins on the schematic and TDIS (GND), and got the same error (-233). However we were able to pass the "test connection" if we plug the XDS200 to the BMC JTAG on K2G EVM using the "TI14 Adapter".

At this point we are wondering whether we can have some reference schematic design of the connection between XDS200 and any DSP SoC, using only the most basic pins (GND, TDO, TDI, TCK, TMS, VTRef).

Thank you,

YW