Other Parts Discussed in Thread: LM5021, UC3844

Hello,

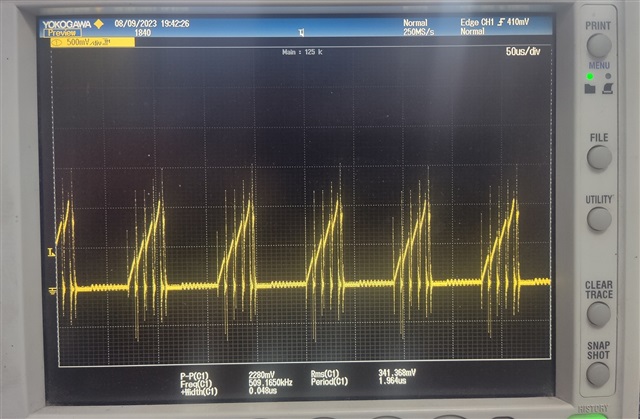

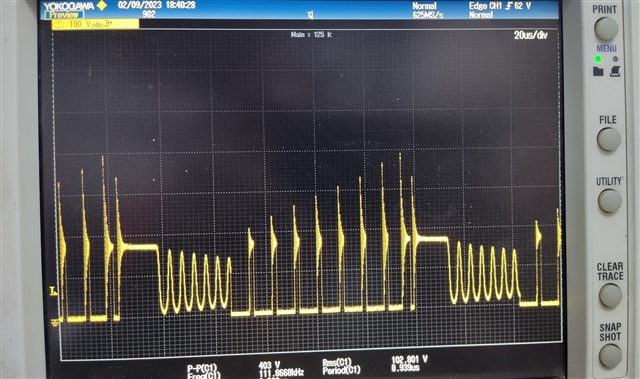

I'm using the TI reference design PMP11329 for one of my power supply design with the output of 18V, 3.6A. I'm able to get till 2A of output but the drain waveform oscillates or the entire loop. The drain waveform looks like below. Switching frequency is currently 100kHz. Initially I tried with 150kHz also.

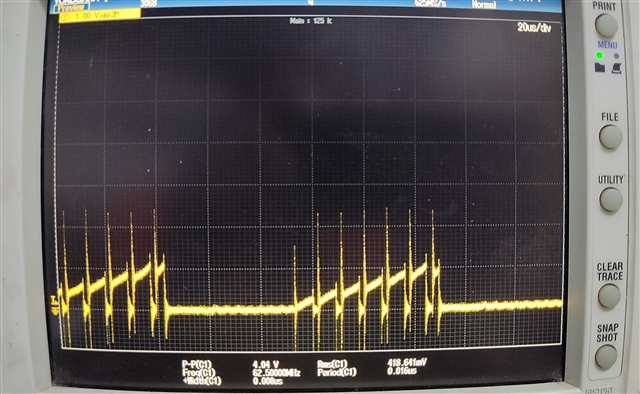

And my current sense waveform looks like below with 500mohm sense resistor.

Kindly help me to solve the issue. Thanks.