Other Parts Discussed in Thread: LM5020, TPS3808

Hi TI,

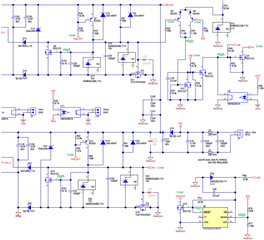

Is the reference design of PMP20859 able to output Vout with only Aux 48Vdc input and with disconnected PoE input? The reason asking this is because Vout would be 0V initially when PoE and Aux input are disconnected respectively. When only Aux input is connected, Q9 'gate' would be high and pull 'SS' to low, which subsequently prohibits U7 to operate and output Vout. This condition would not happen if PoE input and Aux input are connected, and then PoE input is disconnected. Because Vout is ON and pulls down Q9 'gate'.

Regards,

KK