Other Parts Discussed in Thread: LM5109

Hi,

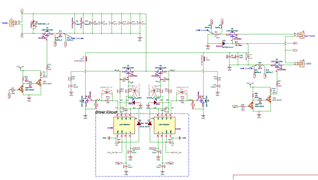

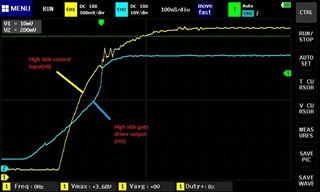

I am developing a battery charger based on TIDA-010042 old reference design(not GaN reference design) with slight modifications. Please see the attached schematic of interleaved buck . While testing the hardware, I have observed that high side gate driver output from driver LM5109 is starting before the HI signal from the microcontroller and there is rise time of . Waveform is also attached. But this issue is not seen for the low side gate output. Low side gate driver output is perfectly following the low side control input from microcontroller. To verify, I have tested the reference design board and the issue is present there also. I am not able to understand the reason behind this issue.