Other Parts Discussed in Thread: SFRA

Hello,

Need some help related to TIDA-010062.

I tested Lab 4 after disabling the overcurrent protection from line 163 of ttplpfc_user_setting.h file

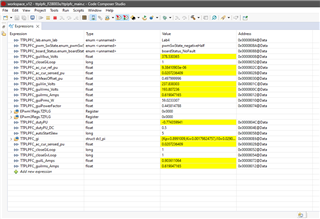

And was correctly able to get the output voltage of 390V(380 in the watch window) and the output current on the load was showing to be around 0.2.

(Load was set at 0.2A in CC as per the test process mentioned in the TIDUET7G)

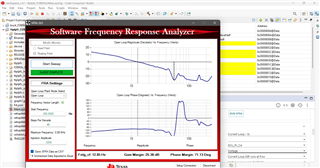

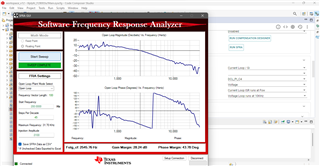

I also checked the SFRA for current loop and voltage loop, the SFRA readings looks fairly stable (kindly check attached screenshots)

However, while trying to increase/set the load current other than 0.2 Amps from load side in CC mode, the load current does not change and remains constant at 0.2Amps.

Why am I seeing such behavior?

Regards,