Other Parts Discussed in Thread: LM62460

Hi,

I'm not really using PSpice usually so I'm a bit unfamiliar with the software, but decided to give it a try to see how far I can get.

I checked this document ( https://www.ti.com/lit/pdf/sluaa51 ) which highlights how to do a loop stability test for a buck converter like the LM62460 on PSPice.

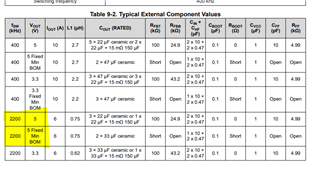

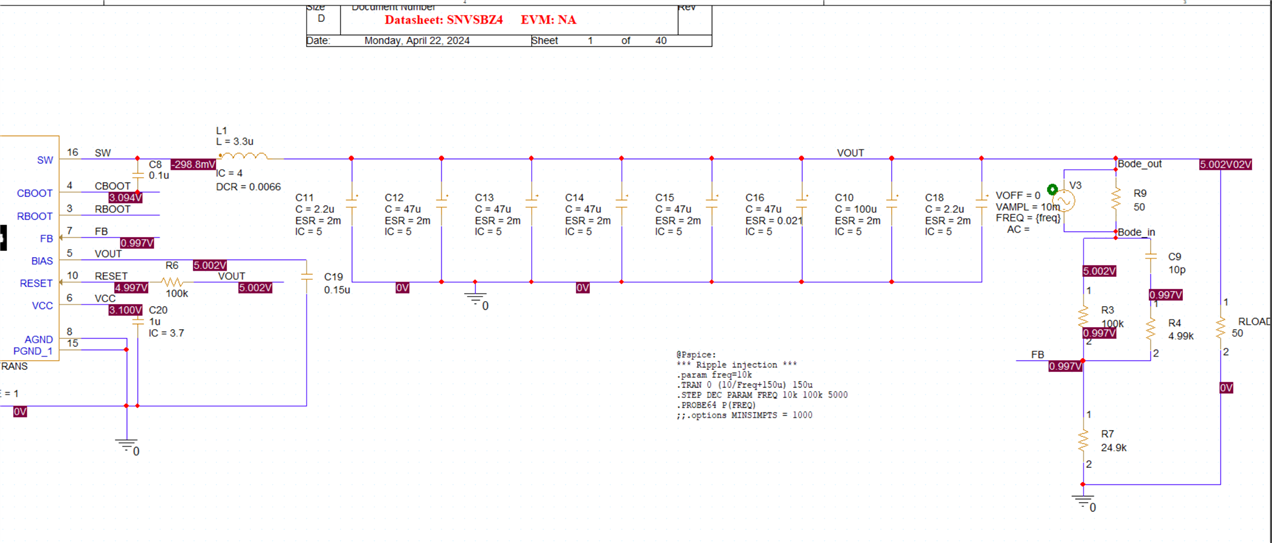

I did this to attempt to reproduce the example :

I get incredibly long simulation times. In fact it seems the thing is still at 0% after simulating for 2 hours in the simulation manager. Simulated only 10ms and it takes hours which just make the simulation completely unusable for rapid preliminary testing.

The "V3" source I assume in a VSIN source? I put the FREQ frequency sweeping from 10kHz to 100kHz with huge 5kHz frequency steps, yet the thing still takes forever.

Since the .TRAN directive is present, I used "Bias point" simulation profile and it seems after calculating the bias point the simulation goes on to transient analysis.

Am I doing this correctly or is the tutorial outdated? Seems the PSPICE for TI is a bit different from the PSpice UI inside shown in the PDF.

Could I get some help from TI to make this work and render correctly a bode plot with phase and gain?

Cordially