Tool/software:

Hi team,

My customer is having a crystal-related issue.

What they are trying to do

- ensure the internal oscillator is off

- route the crystal signal to DIO12 for a buffered output

- set a GPIO (DIO20) high

- enable the external crystal

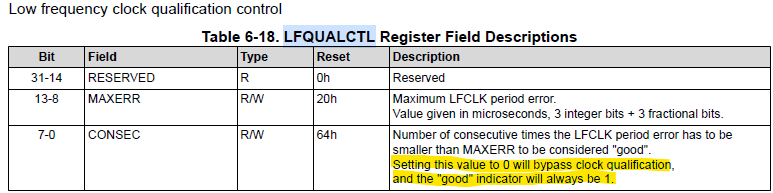

- set DIO20 low when the appropriate flag indicates that the crystal is good

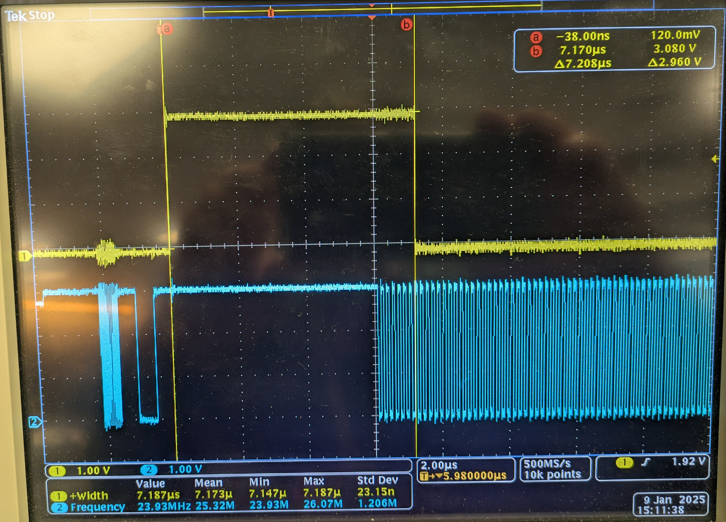

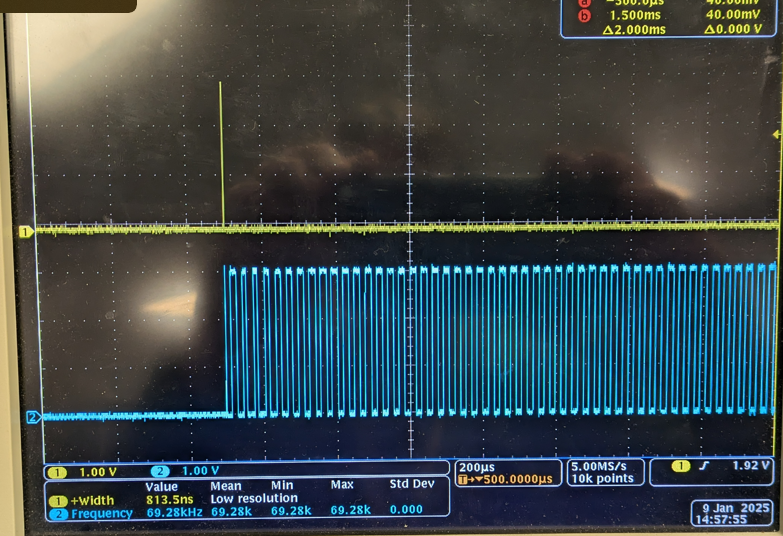

- measure pulse width of DIO20 for startup time

- measure frequency on DIO12

Thanks,