Tool/software:

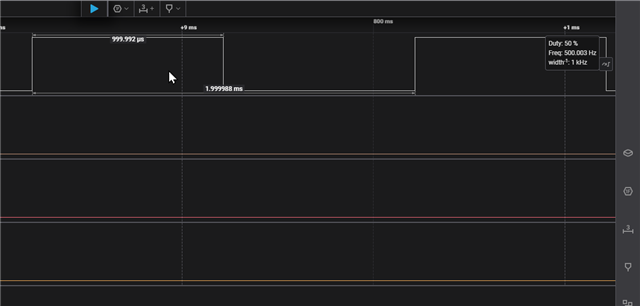

I am having a lot of problems with timing accuracy using the CC2340R5 and BLE Stack.

I have managed to configured DIO19 to output the 48Mhz / 8 = 6Mhz to try and validate the underlying the clock frequency.

This seems to vary from 6.0007 Mhz to 5.952 Mhz. I am really trying to setup this Application to perform some realtime processing, hence I am looking for accurate time domain.

A few questions on this device which I can't work out from the Datasheet.

1) Does the ARM core actually run of the HFEXT 48Mhz crystal - or does it always using the less accurate internal RC Oscillator?

2) I've tried utilising the HFXT Cap Array adjustments - but no real change with those. The reference design from TI shows not to use load capacitors on the crystal itself, maybe I should just try that.

Any support on this would be really helpful.

For anyone else trying to output the clock here is the code snippet I've used. (Placed after Board_Init() )

/* Start of 48Mhz CLK Debugging */

// drive output low first

GPIO_setConfig(19, GPIO_CFG_OUTPUT | GPIO_CFG_OUT_LOW );

// Conigure the IOC.IOC19 PORTCFG MMR to seelct DTB

HWREG(IOC_BASE + IOC_O_IOC19 ) &= ~IOC_IOC19_PORTCFG_M ;

HWREG(IOC_BASE + IOC_O_IOC19 ) |= IOC_IOC19_PORTCFG_DTB ;

//

HWREG(IOC_BASE + IOC_O_DTBCFG) &= ~IOC_DTBCFG_ULLSEL_M ;

HWREG(IOC_BASE + IOC_O_DTBCFG) |= 0x1 << IOC_DTBCFG_ULLSEL_S ; // 0x1 to route CLKD to DTB0

// Enable IOC.DTBOE.EN0

HWREG(IOC_BASE + IOC_O_DTBOE) &= ~IOC_DTBOE_EN0_M ;

HWREG(IOC_BASE + IOC_O_DTBOE) |= IOC_DTBOE_EN0_EN ;

// Seelct which clock (CKMD) to output on DTB0 (DTB[0])

HWREG(CKMD_BASE + CKMD_O_DTBCTL) &= ~CKMD_DTBCTL_CLKSEL_M ;

HWREG(CKMD_BASE + CKMD_O_DTBCTL ) |= (clockSrc) << CKMD_DTBCTL_CLKSEL_S ;

// enable DTB Output

HWREG(CKMD_BASE + CKMD_O_DTBCTL) &= ~CKMD_DTBCTL_EN_M ;

HWREG(CKMD_BASE + CKMD_O_DTBCTL ) |= CKMD_DTBCTL_EN;

/* End of CLK Debugging */