Other Parts Discussed in Thread: TEST2, CC1101

Hello:

I am unable to get the RX FIFO to work properly and not able to figure out what setting is causing the problem. Data that is read back is random garbage.

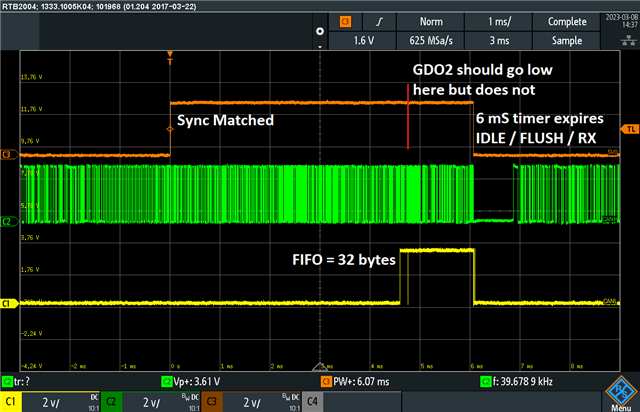

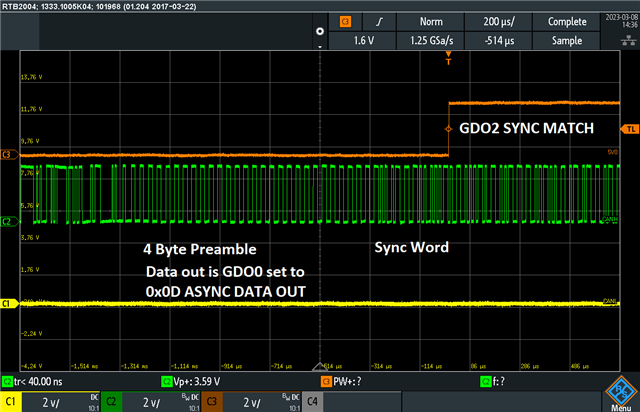

Also with the GDO2 pin configured as 0x06 to go high when a sync word is received which it does do - it however does NOT go low at the end of the message even though the length is set.

I believe these issues are related but can't figure out why / what is causing it.

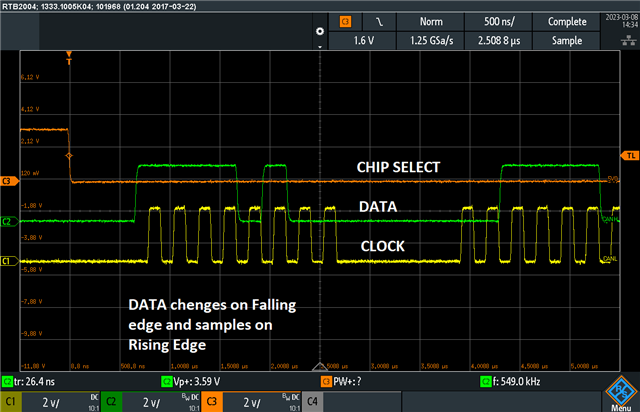

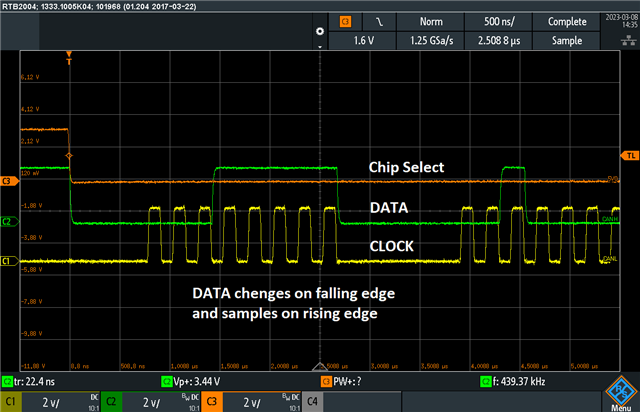

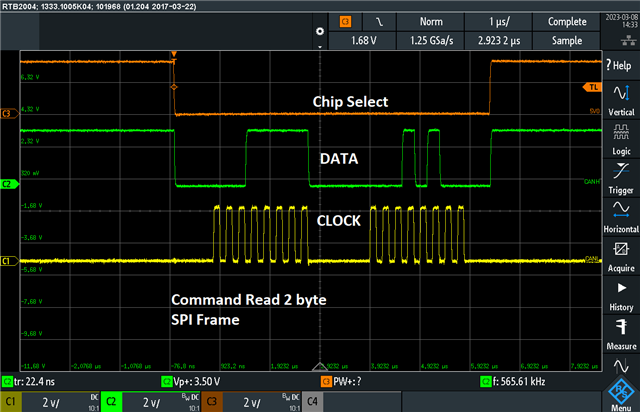

I am able to read config registers and all other items over SPI - just not the RXFIFO so it is not an SPI configuration issue (Mode, timing are all correct.)

because of this I am forced to use the Asynchronous data output and software decode the FSK signal with the microcontroller which I should not have to do.

Please advise on what could cause this IC behavior.

Regards,

Rob Tywlak

BGM Engineering services