hi all,

a customer of mine is facing the following problem:

<<

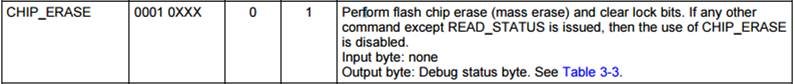

When we run stress test on our device running on CC2530 we get to condition where complete flash is erased. From debug interface specification we can see that chip erase command is quite easy to perform unintentionally – only one “1” is required to execute command while in debug mode.

At the moment we are dealing with this issue by setting pull-up resistor on debug interface clock input line (P2.2). Preliminary tests run with pullup resistor (10kOhm) show improvements but we are not confident to let this solution into production.

Could you ask support for the following questions:

- When looking at CC2530 reference design we see that no protection components are connected to this line. Can you recommend how to additionally protect this line?

- Is there internall pullup present on line P2.2? What is its value? Can it be that in initial startup phase this pullup is not enabled?

>>

I will check which stress test they are performing (I guess ESD or Surge)...

do you have experience of this problem?

is the pull-up resistor a valid solution / patch?

thanks a lot in advance

KR

Vincenzo