Hi

We are using X5777BXGABC processor in one of our design.Where I'm not able to access DDR3L chips(1GB) which has connected to the EMIF2 controller.

I tried connecting JTAG with reduced clock but not able to access any of the DDR registers.

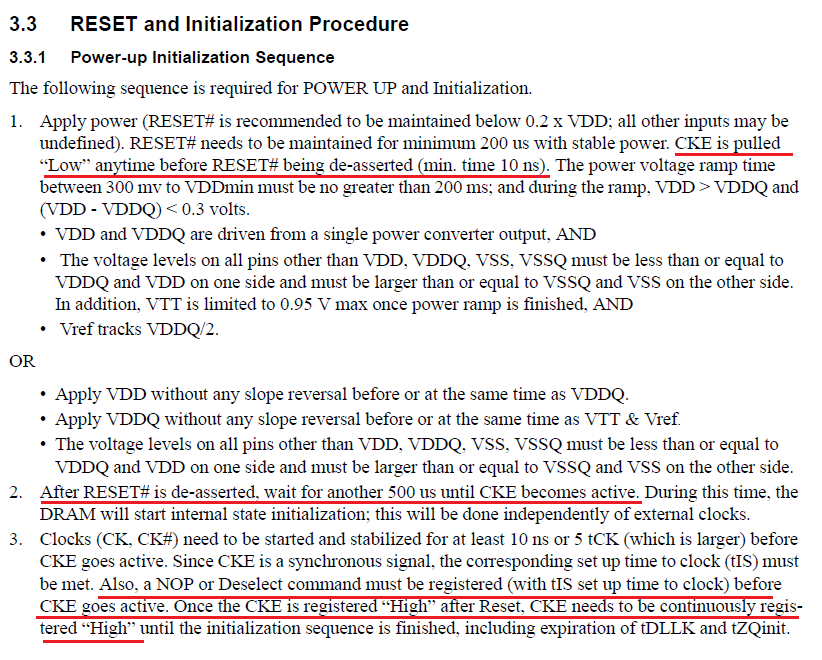

One thing i could observe by probing is that CKE of EMIF2 is not toggling.Its idle as high(Vtt).

Can any one help me further debugging this issue.