Part Number: TDA3

Hi,

I have some questions about SPI of AC timing as follows:

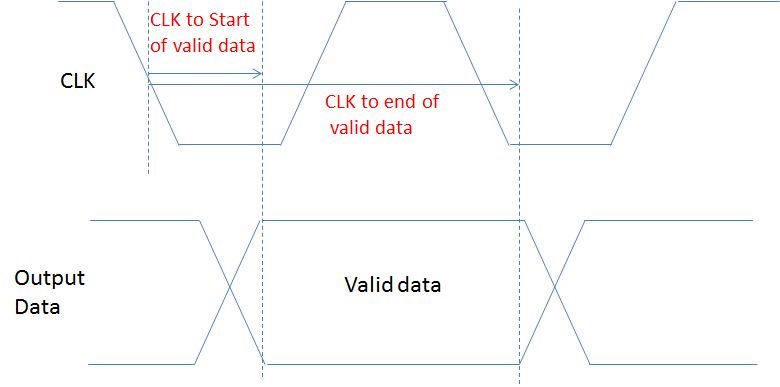

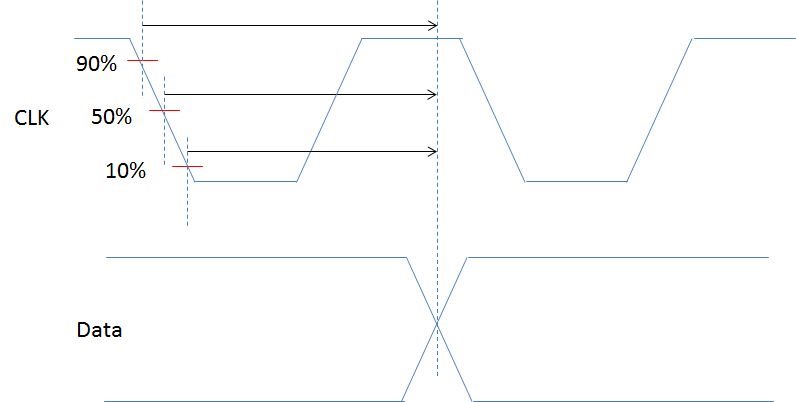

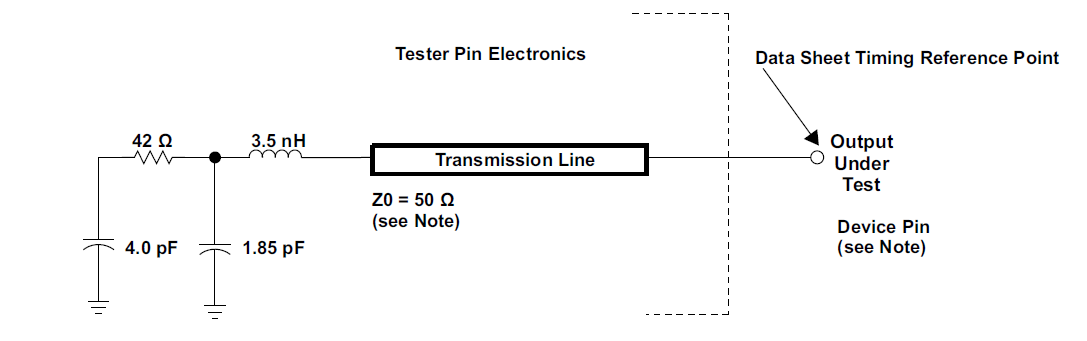

1) Is the AC timing time from the point of 50% of based signal amplitude such as the clock?

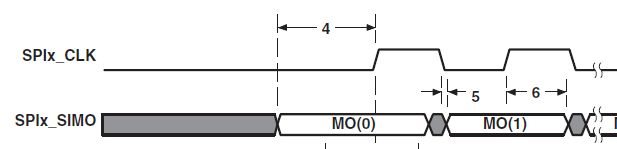

2) SS6 of Figure 7-25 McSPI - Slave Mode Transit

How is SS6 defined setup and hold time of the data signal?

It is defined min and max values. How do I read the setup and hold time of this data from DM?

3) SS7 of Figure 7-25 McSPI - Slave Mode Transit

In PHA=1 case, First SS6 is SS7? However, It is also wrong figure as SS7 if first SS6 is SS7.

Regards,

Kenshow